Japan

サイト内の現在位置を表示しています。

NanoBridge-FPGAによるIoTデバイスの低電力・高性能化

NEC独自の金属原子移動型スイッチ“NanoBridge”を搭載したFPGA(NanoBridge-FPGA)は、電力効率が高く、かつ処理速度が速くなっています。更に、放射線や高温に対する耐性にも優れており、センサー端末の低電力化と高性能化を両立させる技術として、幅広い応用が期待されています。FPGAは半導体スイッチ及びメモリを用いてハードウェア(回路構成)を変更できる集積回路で、CPUと比べて電力効率が高いことが特長です。FPGAで使われる半導体スイッチ及びメモリを、省面積であるNanoBridgeで置き換えることにより、FPGAの電力効率を更に高めることができます。本稿では、NanoBridgeの動作原理、NanoBridge-FPGAの内部構造、及び市販FPGAとの性能比較について述べます。

1. はじめに

社会インフラの保全・メンテナンス、安全・安心な社会、モノづくりの効率化、安全な移動手段の構築などの社会課題が顕在化しています。これらの社会課題に対して、センサーネットワークによるモニタリング、ビッグデータの分析、AI技術を用いた画像認識など、新たなサービスを創出する動きが活発になってきています。これらはクラウド側での情報処理が基本になっていますが、今後、リアルタイム性や通信データ量の削減のために、端末(エッジ)側におけるデータ解析と価値のあるデータの取り出し、送信データの圧縮処理などが重要になってくると考えられます。このような端末側における情報処理は、高い電力性能比、リアルタイム性、ロバスト性などクラウド側における情報処理とは異なる特性が求められます。一方で、情報処理を担う集積回路は微細化の限界、発熱(または消費電力の増大)による性能低下に直面しており、従来の集積回路によるCPUに代表されるノイマン型コンピューティングでは更なる電力性能比(電力効率)の向上が困難になってきています1)。

特定のアプリケーションに特化した専用集積回路(ASIC)は、最も電力効率が高いものの、柔軟性(またはプログラマビリティ)に乏しいこと、また専用集積回路を開発するための費用が高額であるなどの課題があります(図1)。

フィールドプログラマブルゲートアレイ(FPGA)は、内部回路(ハードウェア)をプログラムして、アプリケーションに合わせて処理ブロックや処理フローを回路上に構築できる集積回路であり、CPUと同様に柔軟性を備えています。非ノイマン型のハードワイヤードロジック(布線論理)で情報処理を行うため、ノイマン型のプロセッサに比べて処理能力が高く、これまで以上に端末でのコンピューティングにおいて重要な役割を担っていくと考えられます。また、FPGAは汎用品であるため、集積回路を開発するための費用は不要となります。

FPGAは柔軟性や高い処理能力がある半面、一方で、回路構成を変更するための半導体スイッチと回路構成を記憶する多量の半導体メモリ(SRAM)が搭載されているため、回路面積と待機電力が大きくなるという課題があります。SRAMにおいては、情報の維持に電力が必要となるため、待機電力を消費します。そのためFPGA上に展開される演算に対する論理回路の密度が低く、ビット単位で見た場合の処理電力が大きい問題があります。昨今、FPGAのSRAMを置き換えることができ、情報の保持を必要としない不揮発メモリの研究が、大学の研究機関、及び、各社から提案されています。不揮発メモリとは、磁気メモリ(MRAM)2)や抵抗変化メモリ(ReRAM)3)4)などのメモリ技術を指します。

2. NanoBridge技術

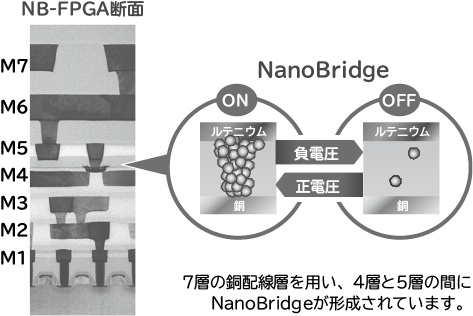

NECでは、半導体スイッチと半導体メモリの両者を同時に置き換えることができる不揮発スイッチであるNanoBridgeを開発しています。NanoBridgeは、ポリマー固体電解質(PSE)を不活性電極であるルテニウム(Ru)と活性電極である銅(Cu)で挟んだ構造をしています(図2)5)。銅電極側に正の電圧を印加すると電極の銅がイオン化し、ポリマー固体電解質内を移動して両電極間に架橋を形成します。その結果、NanoBridgeは高抵抗(オフ)状態から低抵抗(オン)状態へ遷移します。逆に、銅電極側に負の電圧を印加することで架橋を形成する銅原子が銅電極側に回収され、高抵抗状態へと遷移します。

NanoBridgeは繰り返し書き換えが可能で、かつ、各オン・オフ状態を維持するための電力を必要としません(不揮発性)。また、半導体スイッチに比べて負荷容量が小さく(半導体スイッチの10分の1程度)、オン・オフ抵抗差が高い(500Ωと1GΩ)などの電気的特性を備えています。そのため、論理信号を切り替えるための半導体スイッチと回路情報を保持するための半導体メモリとして機能します。また、銅架橋の太さは、数nmと推定されていて、より集積化が進んだデザインルールにおいても回路に組み込むことが可能です。

NanoBridge-FPGAで用いる際には、図2の右側で示すように、2つのNanoBridgeを向かい合わせに接続し、ルテニウム電極側の中間端子に書き込み制御用のトランジスタをつなげた構造としています6)。信号切り替えには、2つのNanoBridgeをともにオンまたはオフ状態とします。オフ状態のスイッチに動作電圧が印加されると、2つのNanoBridge間でその電圧ストレスが分配されます。これに加えて、電圧ストレスの方向に対して2つのNanoBridgeのどちらか一方は、必ずオンからオフへプログラムする電圧方向になるように配置しているため、オフ状態の信頼性を相補的に高めることができます。この相補型NanoBridgeによって、電圧ストレス下の保持寿命は飛躍的に向上しています。また、本構造では、中間ノードを介して個々のNanoBridgeをプログラムするため、オフ信頼性とトレードオフ関係にあるプログラム電圧を低く抑えられます。

3. NanoBridge-FPGAのアーキテクチャ

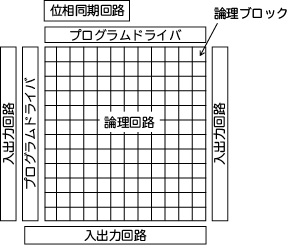

基本的なNanoBridge-FPGAは、アレイ状に配置された論理ブロック、外部と論理信号をやりとりする入出力回路、NanoBridgeをプログラムするためのプログラムドライバ、更にクロック信号を生成する位相同期回路から構成されています(図3)7)8)。論理ブロックは、4つの基本論理エレメント(BLE)、論理信号の接続先を決めるクロスバースイッチから構成されています。BLEは、組み合わせ論理演算が行われるルックアップテーブル(LUT)、順序論理演算が行われるDタイプフリップフロップ(DFF)から構成されており、図4では、NanoBridgeをクロスバースイッチとLUTのメモリに利用しています。クロスバースイッチは、NanoBridgeから構成され、各行のいずれかのNanoBridgeをオンとすることによって、論理ブロックの入力信号の出力先が決まります。出力先は、BLEあるいは隣接する論理ブロックのいずれかが選ばれます。1つのLUTは16個のメモリを備えており、LUTの入力信号に従って選ばれた16個のメモリのうち1つの値が出力されます。LUTのメモリはNanoBridgeから構成されています。クロスバースイッチ及びLUTを構成するNanoBridgeをオンまたはオフにプログラムすることによって回路構成が決まり、ユーザーのアプリケーションが実行できます。

LUTのメモリや配線を切り替えるスイッチで使われている半導体メモリや半導体スイッチをNanoBridgeで置き換えることで、論理ブロックの面積を小さくでき、結果的に、配線長を短くすることによる低消費電力化が実現できます。

4. NanoBridge-FPGAの性能評価

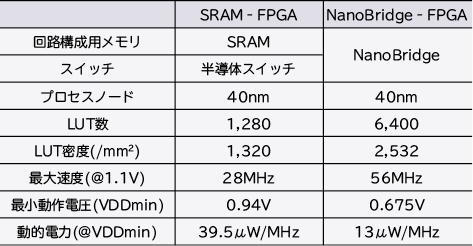

NanoBridge-FPGAの性能評価として、40nmの半導体プロセスで製造された市販のSRAMベースのFPGA9)を用いて、NanoBridge-FPGAとの性能の比較を行いました10)11)。SRAM-FPGAにおいても論理回路にLUT及びDFFが用いられ、LUT数により論理回路の規模を比較することができます。同じ40nmの半導体プロセスで作製されたNanoBridge-FPGAの論理回路の密度は、このSRAM- FPGAに比べて2倍です。NanoBridgeを用いることで論理回路が占める面積を小さくすることができています。

両方のFPGAに1kゲート規模の16ビット算術論理ユニット(ALU)のベンチマーク回路をマッピングしました。ベンチマーク回路は、命令デコーダ及び入力信号発生器を含み、FPGAの論理回路のなかで332個のLUTと73個のDFFが使用されます。マッピングされた16ビットカウンタによって生成されるカウントアップ信号は、ALUのオペランドとしての入力となります。同様にマッピングされたワンホット信号発生器を用いて28個の各命令を周期的にアクティブな状態にします。

NanoBridge-FPGAの回路構成は、所定のNanoBridgeをオンまたはオフにプログラムすることで決まります。NECでは、アプリケーション回路からオン・オフ情報を生成するための設計ツールを準備しています。アプリケーション回路はRTLで記述され、作成したFPGAツール群8)を用いることでオン・オフ情報が生成されます。まず、RTL記述から論理合成ツールによりゲートレベルのネットリストを得ます。その後、クラスタパッキングツールによりネットリストを4入力LUTに変換し、更に、配置配線ツールを使用してLUT間の配置及び各回路の接続を決め、回路構成情報が生成されます。また、アプリケーション回路が実装されたNanoBridge-FPGAへの入力信号パターンに対する出力信号パターンをVerilogテストベンチにより生成し、半導体テスタでNanoBridge-FPGAの動作と整合することで、正しく動作しているかを検証します。本動作検証により、動作電圧領域、信号遅延、更に動作電力を半導体テスタで測定しました。

最小動作電圧は、SRAM-FPGAでは0.94Vであるのに対してNanoBridge-FPGAは0.675Vと、低い電圧まで動作します。最大速度は、標準的な動作電圧である1.1VにおいてSRAM-FPGAと比較して2倍の高速動作が可能です。動的電力はSRAM-FPGAが39.5μW/ MHzであるのに対して、13μW/ MHzと3分の1程度です(表)。これらの性能の差は、主に、NanoBridgeの小さな負荷容量や、論理回路の面積が縮小して配線長が短くなること、つまり、配線での負荷容量も減っていることに起因しています。

表 NanoBridge-FPGAと市販低電⼒SRAM-FPGAとの性能⽐較

5. 過酷環境下での動作

IoT機器は、過酷環境下に設置されることが想定されます。ここでは、高温や放射線に対する耐性について述べます。

高温下では、トランジスタのオフ電流が温度に対して指数関数的に変化するのに対して、NanoBridgeのオフ抵抗の変化は小さく抑えられます。そのため、環境温度が高い場合においてもSRAM-FPGAと比較して、待機電力の増大が少ないという利点があります。また、NanoBridge- FPGAは-50℃から150℃まで正常に動作することを確認しています12)。

NanoBridgeは、放射線への耐性も備えています。SRAMは電荷数の違いによって、オンとオフ状態を表現しています。SRAMを含む集積回路に高いエネルギーの放射線が入射すると、半導体基板中で放射線がシリコン原子と衝突して電荷を発生させます。発生した電荷がSRAM上の電荷を乱し、オンとオフの状態が反転する不具合が知られています。NanoBridgeは物理的な銅架橋の有無によってオンとオフ状態を実現していることから、放射線により発生する電荷によって状態が変化することはありません。

放射線に対するNanoBridgeの耐性は、日本原子力研究所の重イオン照射施設を用いて評価しました。本評価では、128k個のNanoBridgeへ高エネルギーの重イオン(キセノン及びクリプトンイオン)を照射し、オン・オフ状態の変化を調べました。キセノン及びクリプトンの線形エネルギー遷移は、チップ表面でそれぞれ68.9及び40.3MeV/(mg/cm2)であると推定されます。実験の結果、 いずれのイオン照射前後においてもオン・オフ状態の変化は観測されませんでした。放射線への耐性はSRAMに比べて格段に高く、更に放射線への耐性があるフラッシュメモリと比べても少なくとも100倍以上でした。

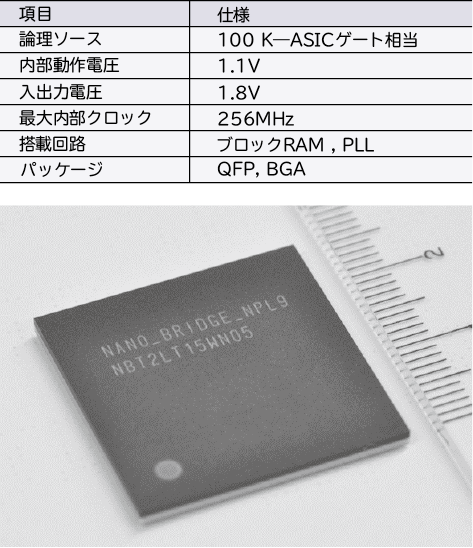

2018年度には、NanoBridge-FPGAは、革新的衛星技術実証プログラムを通じて、軌道上で評価する予定です13)。2018年にイプシロンロケットにより、NanoBridge-FPGAを軌道上に投入します。図5に、本評価で用いられるNanoBridge-FPGAを示します。FPGAには画像圧縮アプリケーションや、放射線への耐性を評価する回路を実装します。カメラで撮影したフルHD画像にNanoBridge-FPGAで圧縮処理を行い、地上局に画像をダウンリンクして不具合がないか評価する予定です。NanoBridge-FPGAへは前述した回路の書き込みを行い、熱サイクル試験、振動試験などの地上試験を実施し、NanoBridgeのオン・オフ状態が変化していないことを確認済みです。本プログラムは、宇宙航空研究開発機構(JAXA)と共同で実施しています。

6. まとめ

低電力の不揮発性FPGAは、使える電力に制限のある端末でのアプリケーション向けに実証されています。 配線切り替え用スイッチとLUTメモリにNanoBridgeが用いられたFPGAは、40nmの同じ技術ノードで製造された従来のSRAMベースのFPGAと比較して、2倍のロジック密度、2倍の動作速度、3倍の動的電力の性能を示します。 開発されたNanoBridge-FPGAは、端末における高性能・低電力コンピューティングを行うのに最適です。

7. 謝辞

本研究の一部であるこの成果は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の助成事業「100万LUT規模原子スイッチFPGAの開発」の結果得られたものです。デバイス試作に関しては、国立研究開発法人産業技術総合研究所スーパークリーンルームステーションにご協力いただきました。感謝いたします。

参考文献

- 1)

- 2) Daisuke Suzuki et al.:Fabrication of a 3000-6-input-LUTs embedded and block-level power-gated nonvolatile FPGA chip using p-MTJ-based logic-in-memory structure,VLSI Technology,2015

- 3) Young Yang Liauw et al. :Nonvolatile 3D-FPGA with monolithically stacked RRAM-based configuration memory,Solid-State Circuits Conference Digest of Technical Papers (ISSCC),2012

- 4)

- 5) Munehiro Tada et al. :Polymer solid-electrolyte switch embedded on CMOS for nonvolatile crossbar switch,I IEEE Transactions on Electron Devices ,Volume 58,Issue 12,pp.4398-4406,2011.12

- 6) Munehiro Tada et al. :Highly reliable, complementary atom switch (CAS) with low programming voltage embedded in Cu BEOL for Nonvolatile Programmable Logic”,Electron Devices Meeting (IEDM), 2011

- 7) Makoto Miyamura et al. :Low-power programmable- logic cell arrays using nonvolatile complementary atom switch,Quality Electronics Design (ISQED),2014.

- 8) Makoto Miyamura et al. :0.5-V Highly Power-Efficient Programmable Logic using Nonvolatile Configuration Switch in BEOL,2015 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays,pp.236-239,2015.

- 9)

- 10) Yukihide Tsuji et al. :A 2× logic density Programmable Logic array using atom switch fully implemented with logic transistors at 40nm-node and beyond,VLSI Circuits,pp.16-17,2016.6

- 11) Xu Bai et al. :A low-power Cu atom switch programmable logic fabricated in a 40nm-node CMOS technology,VLSI Technology ,2017.6

- 12) Makoto Miyamura et al. :NanoBridge-Based FPGA in High- Temperature Environments,IEEE Micro,Volume 37,Issue 5,pp.32-42,2017.10

- 13)

執筆者プロフィール

システムプラットフォーム研究所

主任研究員

システムプラットフォーム研究所

主任研究員

システムプラットフォーム研究所

主任

システムプラットフォーム研究所

技術主幹

システムプラットフォーム研究所

主任研究員

国立研究開発法人 科学技術振興機構 研究開発戦略センター:戦略プロポーザル 革新的コンピューティング,2018.3

国立研究開発法人 科学技術振興機構 研究開発戦略センター:戦略プロポーザル 革新的コンピューティング,2018.3