Japan

サイト内の現在位置

AIプラットフォーム

テクノロジーグループ2021年2月1日

データサイエンス研究所AIプラットフォーム・テクノロジーグループは、社会のデジタル変革の加速に向けて、膨大な計算能力が求められるAI技術を圧倒的に高速化し、AI技術を社会の隅々まで浸透させることを目標に研究開発を行っています。

- 様々なプラットフォームを適材適所で利活用し、クラウドからエッジまで、あらゆる環境においてAI技術の高速化を実現します

- AI技術の抜本的な高速化に向け、人間の脳を模倣した、従来とは全く異なるプラットフォームの研究も行っています

研究テーマ紹介

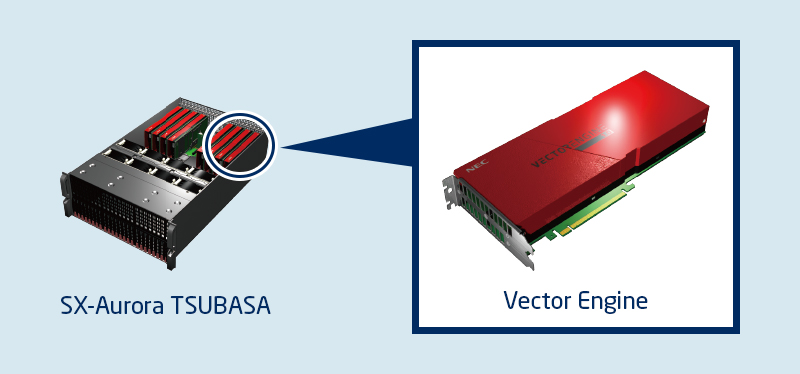

ベクトルコンピューティング

NECは独自のベクトル型コンピュータ「SX-Aurora TSUBASA」を提供しています。従来、ベクトル型コンピュータは大型のスーパーコンピュータとして利用されていましたが、SX-Aurora TSUBASAは「Vector Engine」と呼ばれるPCIeカードの形でベクトルプロセッサを実装することで、幅広い価格・性能レンジで製品を提供しています。これにより、スーパーコンピューティング以外の幅広い領域でも応用が期待できます。

そこで我々は、SX-Aurora TSUBASAを活用しAI処理を高速化する研究を行っています。

具体的には、統計的機械学習を高速化に実行するミドルウェアFrovedisをオープンソースとして開発しています。本ミドルウェアはベクトル型コンピュータの特性を生かしつつ、複数カード、サーバにまたがるVector Engineを並列に利用することで、高速化を実現しています。

また、Deep Learningのベクトル型コンピュータ向け高速化についても研究を進めています。その成果は、Deep Learning向けミドルウェアとして広く使われているTensorFlowのSX-Aurora TSUBASAへの移植として提供しています。

それ以外にも、AIを利用する数々のアプリケーションの高速化や、Simulated Annealingなど組合せ最適化問題への適用についても研究を行っています。

関連情報

受賞履歴

Masahito Kumagai (Tohoku Univ), Kazuhiko Komatsu (Tohoku Univ), Fumiyo Takano (NEC), Takuya Araki (NEC), Masayuki Sato (Tohoku Univ) and Hiroaki Kobayashi (Tohoku Univ), "Combinatorial Clustering Based on an Externally-Defined One-Hot Constraint", The Eighth International Symposium on Computing and Networking (CANDAR'20), 2020. Best Paper Award

Z. Tian (HKUST), H. Yokoyama (NEC) and T. Araki (NEC), "Parallel Latent Dirichlet Allocation using Vector Processors," IEEE High Performance Computing and Communications (HPCC), 2019. Best Paper Award.

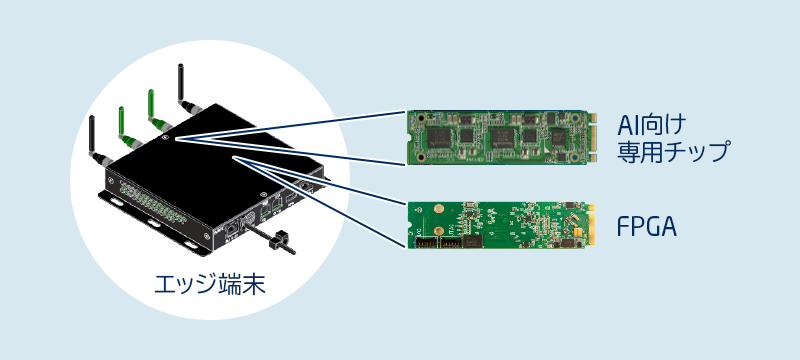

エッジAIコンピューティング

社会のデジタル変革を現実のものにするためには、複雑なAI処理をそれぞれ与えられた制限時間内に(リアルタイムに)実行しなければなりません。しかしながら、従来の汎用サーバのみではリアルタイム処理が実現できなくなり、FPGA、GPU、アプリケーションに特化した専用LSI(Application Specific Integrated Circuit; ASIC、Application Specific Standard Product; ASSP)といったアクセラレータをアプリケーションの特性に応じて適材適所に活用することが求められます。特に、電力や設置要件に厳しい制約があるエッジにおいては、AI処理を効率的に行うことが益々重要になります。そこで、我々は、長年培ったアクセラレータ活用技術を適用し、Safer Cities領域におけるセーフティ事業に活用される監視AIや, Value Chain Innovation領域における製造向け事業に活用される画像検知AIなどの領域において、エッジでのAI処理を圧倒的に高速化する研究を行っています。

受賞履歴

Salita Sombatsiri, Seiya Shibata, Yuki Kobayashi, Hiroaki Inoue, Takashi Takenaka, Takeo Hosomi, “Parallelism-Flexible Convolution Core for Sparse Convolutional Neural Networks”, The 21st Workshop on Synthesis And System Integration of Mixed Information technologies(2018) Outstanding Paper Award.

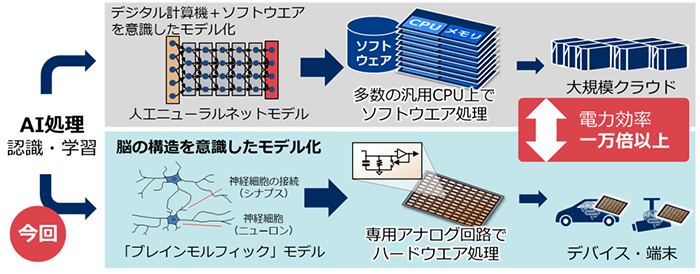

脳型コンピューティング

これまでのコンピュータの性能向上を支えてきたムーアの法則による半導体の高性能化が限界を迎えつつあります。その中で、これまでの計算原理とは異なる全く新しい計算方式によって高性能化を図る取り組みとして、我々は脳型コンピューティングに取り組んでいます。脳のニューロン・シナプスの挙動に学び、それらを効率的かつ極めて低電力で実現する方式の研究を、東京大学と連携して取り組んでいます。これまでのデジタル処理による複雑な計算による処理ではなく、脳を真似たスパイキングニューラルネットワークをデジタルとアナログが混在したハードウェア・アーキテクチャによって実装することで低電力化する研究を実施しています。また、さらに脳が持つ極めて柔軟な判断能力を実現することにも、大阪大学と連携してチャレンジしています。

論文

- Yusuke Sakemi (NEC), Kai Morino (Univ. Tokyo), Timothee Leleu (Univ. Tokyo) and Kazuyuki Aihara (Univ. Tokyo), "Model-size reduction for reservoir computing by concatenating internal states through time," Scientific Reports 10, 21794 (2020).

- Masahito Kumagai (Tohoku Univ), Kazuhiko Komatsu (Tohoku Univ), Fumiyo Takano (NEC), Takuya Araki (NEC), Masayuki Sato (Tohoku Univ) and Hiroaki Kobayashi (Tohoku Univ), "Combinatorial Clustering Based on an Externally-Defined One-Hot Constraint", The Eighth International Symposium on Computing and Networking (CANDAR'20), 2020.

- 荒木拓也, 大野善之, 石坂一久: ベクトルプロセッサを用いたAI処理の高速化, 電子情報通信学会誌, Vol. 103, No.5, pp.529-534, 2020

- L. Feng (HKUST), H. Igarashi, S. Shibata, Y. Kobayashi, T. Takenaka (NEC) and W. Zhang, "Real-time Detection and Tracking using Hybrid DNNs and Space-aware Color Feature: from Algorithm to System," The 5th Asian Conference on Pattern Recognition (ACPR2019)

- J. Li, F. Wang, J. Qiu (Unv. Indiana), T. Araki (NEC), "Generalized Sparse Matrix-Matrix Multiplication for Vector Engines and Graph Applications," SC19 Workshop on Memory Centric High, 2019

- Y. Ideguchi, N. Kamiya, M. Tawada and N. Togawa, "Effective Partitioned Implementation for Successive-Cancellation Polar Decoder," IEEE International Midwest Symposium on Circuits and Systems (MWSCAS) 2019

- Z. Tian (HKUST), H. Yokoyama (NEC) and T. Araki (NEC), "Parallel Latent Dirichlet Allocation using Vector Processors," IEEE High Performance Computing and Communications (HPCC), 2019

- H. Li (HKUST), H. Yokoyama (NEC) and T. Araki (NEC) : Merge-based parallel sparse matrix-sparse vector multiplication with a vector architecture, Proc. 20th International Conference on High Performance Computing and Communications, pp. 43-50, June 2018

- H. Igarashi, F. Takano, T. Takenaka, H. Inoue and T. Moriyoshi, "Parallel Rate Distortion Optimized Quantization for 4K Real-time GPU-based HEVC Encoder," IEEE International Conference on Visual Communications and Image Processing (VCIP) 2018

- T. Araki: Accelerating machine learning on sparse datasets with a distributed memory vector architecture, Proc. 16th IEEE International Symposium on Parallel and Distributed Computing, pp. 112-121, July 2017.

お問い合わせ

GitHub: Frovedis: NEC framework of vectorized and distributed data analytics

GitHub: Frovedis: NEC framework of vectorized and distributed data analytics