Japan

サイト内の現在位置

機能一覧

解析モデリング

プレーンメッシュモデル

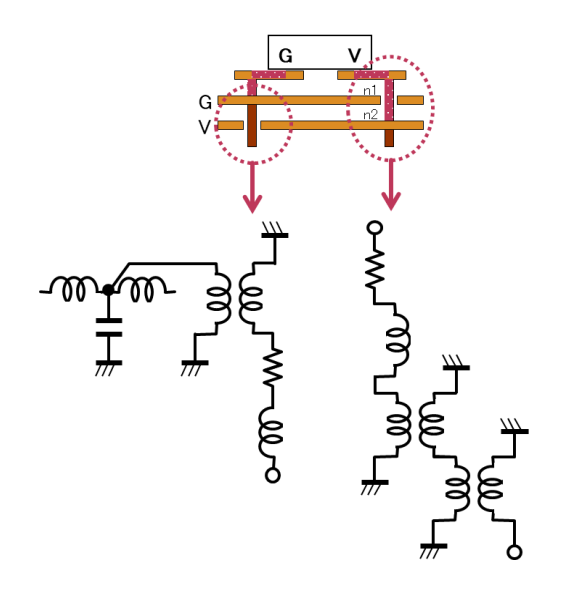

プリント基板の電源・GNDをPEEC(Partial Element Equivalent Circuits)法を用い、RLCG等価回路を生成します。

これにより高速な解析が可能となります。また、このモデルに、LSI及びICパッケージモデル設定GUIにより入力したLSIやヴィアのモデルが付加されます。

拡大する

拡大するキャパシタモデル

キャパシタのモデリングにはキャパシタの寄生インダクタンスや寄生抵抗だけではなく 引き出し配線やヴィアのインダクタンスおよび抵抗成分が重要になります。

PIStreamは、既配線のプリント基板データの場合、キャパシタに接続する引き出し配線や ヴィアの特性を考慮します。また未配線のプリント基板のデータの場合、キャパシタ部品単独の 特性に、あらかじめ設定された引き出し配線やヴィアの特性を加えてモデル化します。

LSIおよびICパッケージモデリング

励振源設定でLSIを指定した場合、指定LSIの電源ピンを検出し励振源モデルを電源ピン数に合わせて分割し、PCBとLSI/ICパッケージモデルを適切に接続します。

LSIの電源ピンがn箇所ある場合、n分割します。

LSIの電源ピン毎にプレーンと接続する位置を検出し、それぞれの接続位置に対し 電源ピン数で分割したLSI/ICパッケージモデルを接続します。

- ※PI対策は、LSI (ICパッケージ) がプレーンに接続する箇所の周辺にキャパシタを置くことが有効です。

LSIの電源ピンがn箇所ある場合、n分割します。

ヴィアモデル

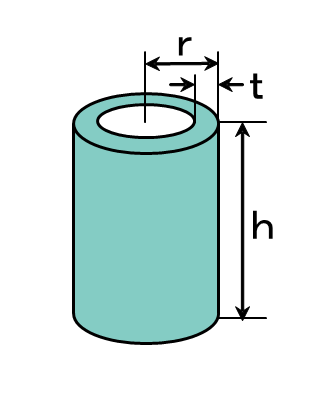

PI解析において、ヴィアはインダクタンスとしての振舞いと、プレーンキャビティー(プレーンペア)間の エネルギー伝達の働きをします。

PIStreamでは、ヴィアの形状から抵抗・インダクタンス値を算出し、ヴィアとプレーンとの接続関係から プレーンキャビティー間の伝達特性をモデリングします。

ヴィアの抵抗・インダクタンス値の算出

LSIを「基板+LSI解析」に必要な設定

高さ(h)、半径(r)、メッキ厚(t)より抵抗値、インダクタンス値を算出します。

プレーンキャビティーを考慮したヴィアモデルの抵抗・インダクタンス値の算出

LSIを「基板+LSI解析」に必要な設定

メッキプレーンとの接続関係に合わせたキャビティー(プレーンペア)間エネルギー伝達モデルを生成します。