Japan

サイト内の現在位置を表示しています。

ASIC・FPGA設計向けC言語ベース高位合成ツール CyberWorkBench

トピックス

ツール認証(ISO26262)を取得しました

CyberWorkBenchはこの度、機能安全規格「ISO26262」のツール認証(SGS-TÜV認証)を取得しました。

ISO26262は自動車産業における機能安全の国際規格となっており、本規格取得によりISO26262に準拠した開発プロセスにおいてCyberWorkBenchを利用できるようになりました。

C言語ベース高位合成ツール CyberWorkBenchとは

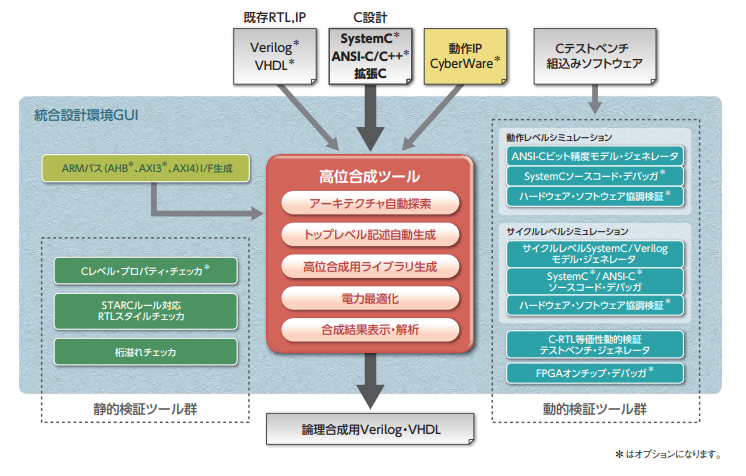

ーASIC・FPGA設計向けC言語ベース高位合成ツールCyberWorkBenchは、C言語からの高位合成と、C言語レベルの機能・タイミングデバッグや、形式検証を行える統合設計ツール群ですー

AI/IoTの進化でモノにマイコンが組込まれ、制御とインターネットで通信できるようになりましたが、さらに装置の軽量化、省電力化、価格削減も叫ばれ、高機能/高消費電力のマイコンから低消費電力のマイコン+FPGAに変わってきております。

ここで必要になるのがマイコンで動いていたソフトをFPGAに移植する作業です。

CyberWorkBenchは、このソフトをFPGAに移植するためのツールです。

CyberWorkBench導入のメリットとユーザー様導入事例

設計期間短縮8→3ヶ月に削減

ソフトウェア技術者主体の開発体制実現

設計記述量1/10へ削減→使用HW量の大幅削減

監視カメラへのエッジHWの搭載

CyberWorkBenchによるLSIの設計フロー

以下はCyberWorkBenchによるLSIの設計フローです。中核となる高位合成ツールでは、仕様から作成したC言語記述を「動作合成Cyber」に入力することでRTL記述が合成出力されます。

図を拡大する

図を拡大する