# プロジェクトにおける不要電磁波を抑制するプリント板設計技術

鎌田 正浩・高橋 太一・藤巻 憲一

**要旨**

製品のEMI対策には、目に見えないスケジュールへのインパクトや、コストアップへの影響があります。今回、弊社プロジェクト「iP-01」の開発において、EMIに対して従来とは異なるアプローチ手法を用いた結果、コストを抑え、開発期間にも影響を与えることなく製品を開発することができました。本稿ではそのアプローチ手法や、ポイントについて紹介します。

**キーワード**

●回路設計 ●パターン設計 ●EMI対策 ●プロジェクト ●DEMITASNX ●CADVANCE

## 1. はじめに

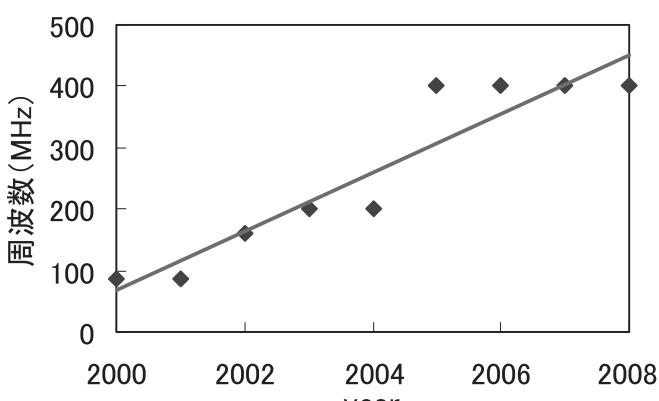

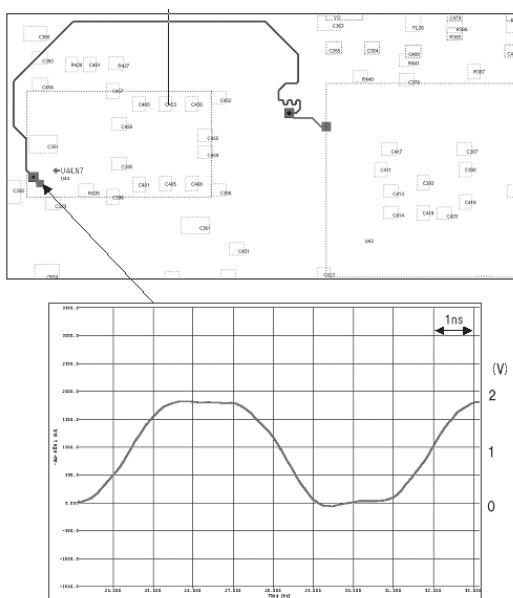

製品を開発し販売するには、製品を設計仕様通りに動作させるとともに、製品から放出される電磁波レベルを規制する規格（EMI規格）以内に収めなければなりません。しかしながら、製品の高性能化へのニーズはとどまるところがなく、それに対応するため、電子回路の動作速度は年々上昇しております（図1）、従来と比較して格段にノイズが発生しやすい状況となっています。短納期での開発が望まれる民生機器においては、ノイズ対策に要する時間とコストが無視できない課題となっています。

今回開発した液晶プロジェクタ「iP-01」では、上記の理由により更に難易度が高くなると予想されるEMI対策にかかる

期間及び対策コストの削減とともに、製品コスト全体をも低減するという目標を掲げて開発しました。結果として、ノイズの発生源であるメイン基板の部品数削減、基板サイズの小型化、層数低減、及びこれらを実現するためのプリント板設計プロセスの大幅な見直しにより、課題を解決することができました。本稿では、プリント板設計プロセスとアプローチ手法に焦点を当てて紹介します。

## 2. 前製品でのEMI対策

### 2.1 開発プロセスについて

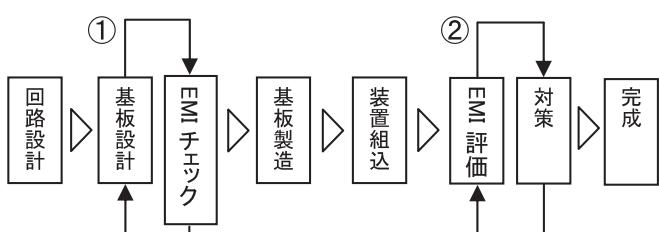

前製品までの開発プロセスは図2の通りです。

プリント板の設計を行う際にEMI抑制支援設計ツール（DEMITASNX）を用い、EMIに関連するさまざまな設計ルールを事前にチェックすることによって、基板製造の前段階で必要な対策を盛り込む設計を行っていました。この開発プロセスでは、図2①で設計の繰り返しが発生しますが、図

図1 AVIOプロジェクト クロックの最高周波数

図2 前製品の開発プロセスの流れ

2②の段階では、装置側で対応が可能となり、プリント板の再設計まで戻ることはあります。

しかし、プリント板設計後にEMIチェックを行うため、電源/グランド面の共振対策は主にバイパスコンデンサなど部品追加で対応しなければならず、基板の小型化（コスト低減）には課題が残っていました。

## 2.2 前製品の基板や構造の課題について

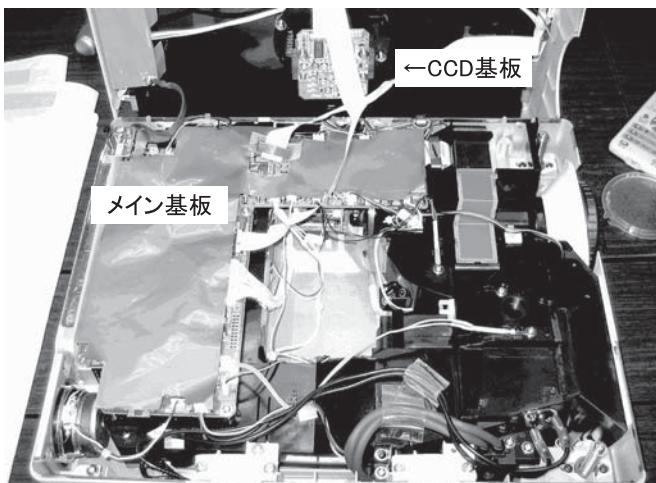

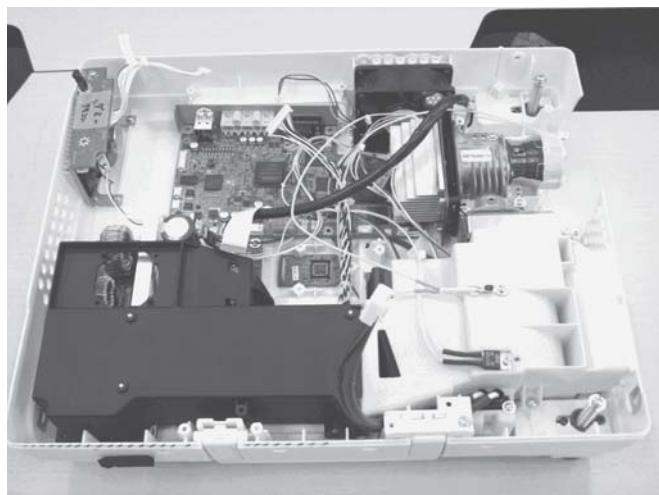

**写真1** に、前製品の内部構造を示します。

前製品を用いてノイズ発生原因を詳細に解析した結果、プリント板のみならず、以下に示す通り、構造的な問題を抽出することができました。

### (1) メイン基板がL字型の変形基板である

複雑な形状の基板は長方形の集まりと考えられ、長方形ごとに共振が発生するとともに互いに影響し合って更に複雑な共振現象を現します。更に重要なことは、電源のコネクタと電力を消費するLSIの距離が長いことです。L型基板の凹部に高周波電流が集中し、基板端がアンテナになってノイズを発生させていることが分かりました（写真1では、基板の上に銅箔の電磁波シールドを貼って対策をしています）。

### (2) CCD基板とメイン基板をつなぐ配線が長い

高速でデータのやり取りがあるところは、配線が長く、グランドが近くになればノイズの原因となります。

写真1 前製品の内部構造

$$E_c = 2\pi \times 10^{-7} \times \frac{i_c f l (K+1)}{d} \text{ (V/m)} \quad (\text{式1})$$

上式は、リターン電流経路のない配線から発生するコモンモードノイズ $E_c$ を求める式です。

コモンモード電流 $i_c$  (A)、周波数 $f$  (Hz)、配線長 $l$  (m)、被測定物とアンテナの距離 $d$  (m)、暗室の床面の反射係数 $K$ としたときのコモンモードノイズ $E_c$  (V/M) です。

この式から配線長 $l$ が長くなるほどコモンモードノイズが大きくなることが分かります。

### (3) メイン基板の下に電源基板がある

メイン基板の下に電源基板が配置されています。メイン基板からは主に高い周波数の電磁界ノイズが、電源基板からは主に低い周波数の磁界ノイズが発生しますが、これらの基板を至近距離におくと空間で電磁結合が発生し、おののの基板に影響を与えます。その結果、メイン基板には単独で存在するはずのない低周波域の磁界が、同様に電源基板に高周波域のノイズが電源基板の2次側、1次側にあるLCフィルタを素通りして電源ケーブルから外部に漏れ、メイン基板に接続されているハーネスからは広域（低周波+高周波域）ノイズが観測されます。

DEMITASNXでメイン基板自体の共振を抑えることはできましたが、上記の観点で装置本体の構造についても対策が必要であることが分かりました。

## 3. iP-01での基板設計への新アプローチ

新製品の「iP-01」のプリント板設計には、第2章第1節・第2節での課題を解決し、更にノイズとコストの低減を両立させるため、対策を行いながら開発を進めるなど、新たな開発アプローチを採用しました。

## 3.1 開発プロセスについて

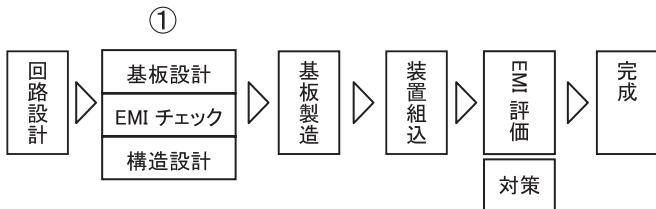

開発のプロセスを 図3 に示します。図2との大きな違いは、回路設計及びプリント板設計段階で、回路機能を満足させる上で必要な部品以外を徹底的に削除したこと（EMI対策部品含めて）、及び複数のプリント板間を接続する配線長をできるだけ短くするための構造を徹底的に見直したことです。

図3 iP-01の開発プロセスの流れ

基板設計段階では伝送線路シミュレータ（Mentor Graphics; HyperLynx）を用いて、高速信号配線の信号波形をチェックしながら配線しました。

ダンピング抵抗は、LSI（信号を出すドライバ側）の出力インピーダンスと信号配線の特性インピーダンスの整合を取り、負荷側から戻ってくる反射波を吸収するために必須となる部品ですが、配線が動作周波数の波長より極端に短い場合や、ドライバ側LSIの出力インピーダンスが配線の特性インピーダンスに見合うほど高い場合は、伝送線路シミュレータで確認した上で削除することがあります。

図4はDDRのコントローラとメモリ間の負荷端の信号波形を伝送線路シミュレータで確認した例です。波形にはオーバーシュート、アンダーシュート、リンクギングなど信号反射

図4 HyperLynxの配線シミュレーション例

の影響が見られず、正しく伝送されていることが分かります。ただし、信号波形の立ち上がり、または立ち下がり時間があるレベルを超えて遅くなると、LSIの電源/グランド間に貫通電流が流れ、ノイズへの影響が懸念されるようになります。

配線ごとにシミュレーション結果を確認しながらパターンを引くので、プリント板設計にかかる期間は長くなりますが、ダンピング抵抗やビーズコアなどノイズ対策部品の要否判断が基板設計を行いながら可能であることと、開発フェーズが進んでからEMI設計を見直すような手戻りが発生しないことが期待できます。

構造設計段階でのEMI設計と同じタイミングで検討することにより、「EMI評価」後の対策に掛かる期間は大幅に削減することが可能です。

### 3.2 新製品iP-01の設計について

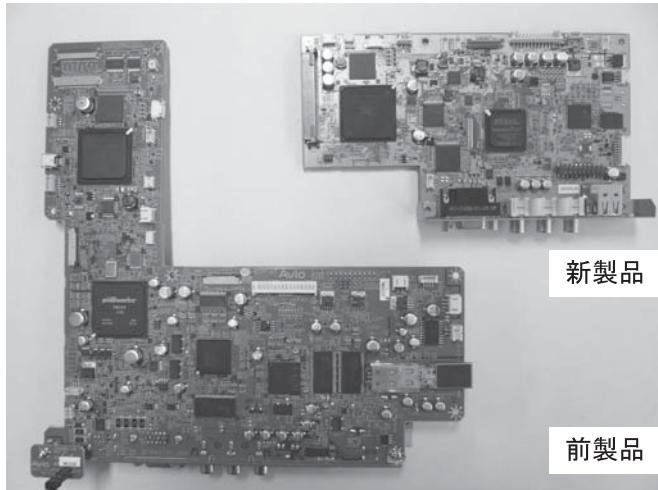

第2章第2節で述べた前製品の課題については、それぞれ以下のように対応しました（写真2）。

メイン基板については、徹底的に部品点数を削減し、基板の小型化を図るとともに、複雑なL字型の基板形状をやめ、シンプルな長方形としました。更に基板間の配線長をできるだけ短くするため、装置レイアウトを見直し、従来長い配線で接続されていたCCD基板を上面ケースから底面に変更することにより、配線長を1/10以下に短くしました。電源基板の配

写真2 新製品iP-01の内部構造

置は、メイン基板を小さくすることにより、電源との重なりをなくし、更に電源ケーブルが最短となるようにレイアウト変更するなど、同様の手法ですべての配線を短くすることができました。機器から発生するノイズを低減し、外部からのノイズの影響を受けにくくするには、機器内の配線をできるだけ短くすることを基本としました。

メイン基板のパターン設計については、第3章第1節のほかに以下の対応を行いました。

#### (1) 電源からLSIまでの配線距離を最短となるように部品配置を行う

電源コネクタと消費電力の大きなLSIまでの距離を構造の許す限り最短にし、電流ループを小さくすることでノイズ発生を低減させました。この電流ループ経路が大きくなればなるほど、そのループ中に含まれるさまざまな回路またはLSIなどの動作が不安定になります。

#### (2) リターン電流経路を確保する

10MHzを超える高速の信号は電磁波として扱わなければならず、基板を設計する際には特別な配慮が必要となります。例えば、高速信号に接する面（別の層）はインピーダンスの低い面でなければなりません。この面がなければノイズは空中に拡散してしまいます。

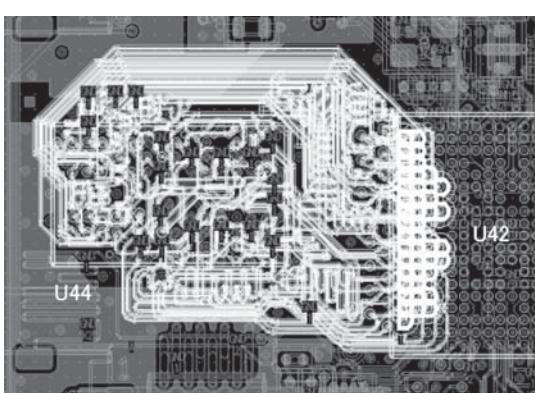

図5はDDR2 (DoubleDataRate2) 及び周辺回路の信号配線が真下にインピーダンスの低いグランド（または電源）面があるかをCADVANCE  $\alpha$  III Knowledge Base Assist Systemを用いてシミュレーションし検証している画面です。

特に多電源の基板では、電源間のスリットによってリターン電流経路が分断されていないかチェックを行いながら設

図5 DDR2の電流ループ

計しなければなりません。

$$E_d = 1.316 \times 10^{-14} \times \frac{i_d f^2 S (K + 1)}{d} \text{ (V/M)} \quad (\text{式2})$$

上式は、リターン電流経路のある信号から発生するディファレンシャルモードノイズ  $E_d$  を求める式です。ディファレンシャルモード電流  $i_d$  (A)、周波数  $f$  (Hz)、電流ループ面積  $S$  ( $m^2$ )、被測定物とアンテナの距離  $d$  (m)、暗室の床面の反射係数  $K$  としたときのディファレンシャルモードノイズ  $E_d$  (V/M) です。この式から電流のループ面積  $S$  が大きくなるほどディファレンシャルモードノイズが大きくなることが分かります。今回の設計では、すべての高速信号についてリターン電流経路が確保されているかを確認しました。

#### (3) 各GNDレベルの電位差を作らない

プリント基板上のGND間の電位差がノイズを発生させる原因（特に氷像ベタパターン部）になることがあります。配線のインダクタンスは、低い周波数では問題ありませんが、動作周波数が高くなるに従ってインピーダンスが増加し、電位差を発生させます。プリント基板の導電部が銅箔でできている限りインダクタンスを0にはできませんが、できるだけ配線長を短くし、適切な場所に内層GNDとの接続Viaを置くなど、インダクタンス低減に配慮しました。参考までに、高速信号では配線幅を広くするより配線長を短くする方がインダクタンスを低減できます。

#### (4) バイパスコンデンサや、ダンピング抵抗の最少の数量と適切な配置を行う

バイパスコンデンサは、LSIまたはICの電源インピーダンスを低減させるために大変重要な役目をします。今回の開発では、PI Stream (ICの電源/GND間インピーダンスのシミュレーションツール) とCADVANCE Knowledge Base Assist System (パソコン自動配置配線ツール) を使って、パソコンの最適容量、位置を決定しました。従来、パソコンといえば  $0.1 \mu F$  を主体に使っていましたが、高い周波数で動作するLSIの電源インピーダンスは、その周波数で最も低くなることが望ましく、その近傍に位置するパソコンはさまざまな容量値が必要であることが分かりました。

また、パソコンは電源/グランド間の面共振を抑える意味でも大変重要です。基板設計段階で共振周波数、及び共振を

写真3 基板面積比較

抑えるためのパソコン容量、位置を特定するため、DEMITASNXを使って設計しました。

#### 4. 結果

今回、開発のプロセスやEMIに関連する基板や構造の課題を見直したことで、電界コンデンサを66個から14個へ、バイパスコンデンサを465個から364個へ、ダンピング抵抗を285個から251個へ削減しました。こうした部品点数の徹底的な削減の結果、基板の面積を約70%小型化（写真3）することができました。更に、終盤の評価と対策の期間が大幅に短縮できました。また、GND間の電圧レベルが小さくなつたため、ノイズが低減し、筐体の導電塗装をなくすことでコストダウンすることもできました。

#### 5. むすび

本稿では、EMI対策で成果を上げた基板設計の開発プロセスと設計段階で考慮したポイントについて紹介しました。今回のアプローチでは、商品開発の初期段階（基板設計）でEMIについて深く考慮すること、及びプリント基板だけでなく構造上の改善によってノイズ抑制とコスト低減が同時に達成できることが分かりました。

最後に、株式会社システムデザイン研究所様には、プリ

ト板設計とシミュレーションの同時進行が可能なツールのご提供と技術サポートに多大なるご協力をいただきました。ここに御礼申し上げます。

#### 執筆者プロフィール

鎌田 正浩

日本アビオニクス

映像・情報福祉機器事業部

映像技術部

映像情報メディア学会会員

高橋 太一

日本アビオニクス

映像・情報福祉機器事業部

映像技術部

マネージャー

藤巻 勝一

日本アビオニクス

映像・情報福祉機器事業部

映像技術部

マネージャー