# 40nmノード CMOSプラットフォーム (UX8)

深井 利憲・池田 昌弘

高橋 寿史・夏目 秀隆

## 要旨

UX8は、NECエレクトロニクスの最先端プロセスであり、最先端露光技術を用いて前世代比2倍のゲート密度を達成し、新規技術を採用して性能改善を行っただけでなくコア、1.8V系、3.3V系トランジスタとSRAM、DRAMのメモリ混載も実現しました。更にUX8は、高速動作から低消費電力アプリケーションに対応するためコアデバイスについて2種、0.9V LOP (Low Operation Power)と1.1V LSTP (Low STandby Power)、を開発し、コアの選択を可能にしたことから、ロジック製品からDRAM混載製品までの幅広いユーザに対応したデバイスプラットフォームを有します。本稿では、UX8で適用した代表的な技術、デバイスラインナップを紹介します。

## キーワード

●LSI ●低消費電力 ●混載メモリ ●SRAM ●DRAM

## 1. はじめに

高集積、低消費電力、低コストのシステムLSIを実現できる40nmノードCMOSプラットフォーム（コード名：UX8）を開発しました。

UX8では、コアトランジスタのゲート長は40nm、ゲート絶縁膜厚は2.0nm未満になります。このような微細なパターンを形成するために、リソグラフィー技術は、最新の露光技術である液浸露光を採用しています。また、ゲート絶縁膜には、55nmノード(UX7LS)で世界に先駆けて採用したhigh-k材料(Hf-doped silicate)をUX8にも適用し、高性能なトランジスタを開発しました。

表にNECエレクトロニクスの90nmノード(UX6)からUX8までの技術をまとめました。

表 世代間技術推移

| process Name      | UX6M/H  | UX7LS             | UX8L/G            |

|-------------------|---------|-------------------|-------------------|

| Node(nm)          | 90nm    | 55nm              | 40nm              |

| Lg(nm)            | 60nm    | 50nm              | 40nm              |

| gate dielectric   | SiON    | Hf-doped silicate | Hf-doped silicate |

| channel direction | ⟨110⟩   | ⟨100⟩             | ⟨100⟩             |

| activation tool   | RTA     | RTA               | MSA               |

| Silicide          | CoSi    | NiSi              | NiSi              |

| Litho. tool       | ArF Dry | ArF wet           | ArF wet           |

UX8は、これまで培ってきた低消費電力対応技術をプラッシュアップし、最小限の新規技術追加で製造コストを抑えつつ、高性能化を実現しました。また、開発当初よりDRAM混載前提の開発を進め、メモリ混載ロジックの先端製品も含めた幅広いユーザに対応したデバイスプラットフォームになっています。

本稿では、UX8で採用した新しい技術、デバイスラインナップを紹介します。

## 2. 高集積化に適したUX8プラットフォーム

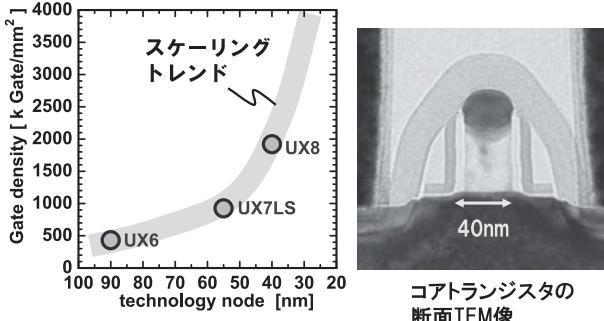

一般的にX方向(Y方向)のシュリンク率(例えばトランジスタピッチや配線ピッチ)はムーアの法則により0.7倍が一般的です。これは面積に換算して $0.7 \times 0.7 = 0.5$ となります。つまり世代が1つ進むと、半分の面積で前世代と同じ機能を半導体チップ上に作りこむことができるということを意味します。NECエレクトロニクスでは、早期に最先端の液浸露光装置を採用し(詳細は本誌pp.65-68「液浸リソグラフィの開発」を参照)、UX8ではコアトランジスタの最小ゲート長40nmと前世代比2倍のゲート密度( $\sim 2,000 \text{ Gate/mm}^2$ )を達成しています(図1)。

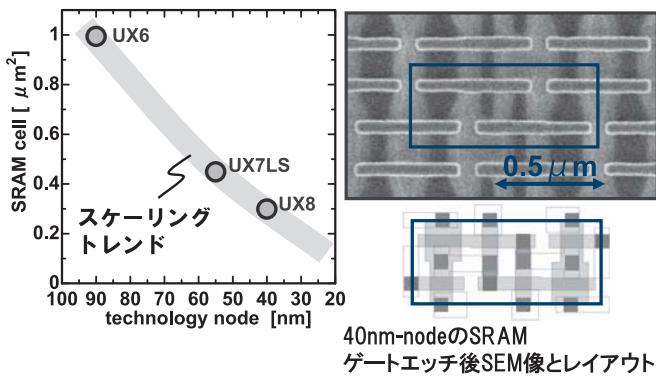

同様にセル面積が $0.3 \mu\text{m}^2$ 未満という高集積に適したSRAMを安定して実現することができました(図2)。

## 次世代CMOS基盤技術

### 40nmノード CMOSプラットフォーム (UX8)

図1 ゲート密度トレンド

図2 SRAM面積トレンド

### 3. 高性能UX8トランジスタ技術

トランジスタ性能は、これまで紹介したような形を縮小するだけでは向上しません。なぜならば、スケーリングしない因子が存在するからです。本項ではスケーリングしない因子をいかなる技術で克服したかを紹介します。

#### 3.1 トランジスタを小さくするための技術

##### —MSA (Milli-Second Annealing) の適用—

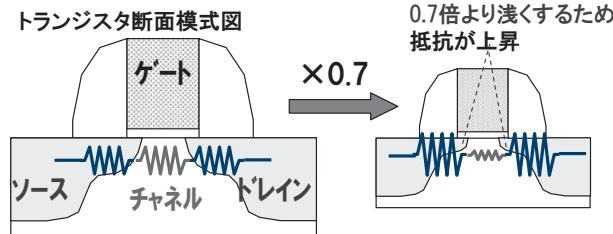

微細化されたゲート長Lで安定したトランジスタ特性を実現するためには、ソース・ドレイン(SD)の不純物<sup>1</sup>分布を浅くする必要があります。一方で、SD領域に導入された不純物の活性化率は飽和傾向にあるので、SDを浅くすると単純にSD抵抗が高くなり、トランジスタ電流駆動能力が低下するという

スケーリングによりチャネル抵抗は小さくなる（良い）が、ソース・ドレインのチャネル側深さをスケーリング以上に浅くするため抵抗が増大（悪化＝スケーリング課題）し、トランジスタの性能を劣化させる。

図3 SD浅接合化の課題

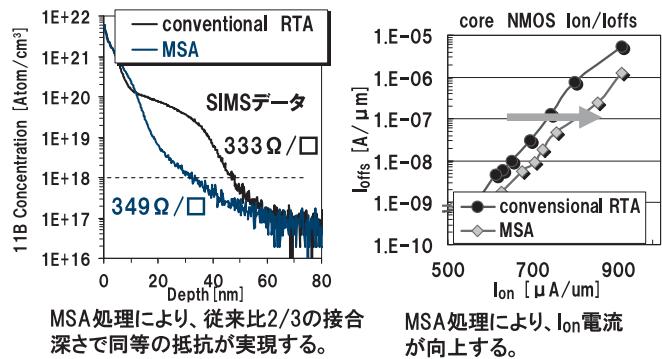

図4 MSAによる層抵抗改善とトランジスタIon向上

問題があります（図3）。

従来のSD不純物活性化熱処理は、1,000～1,100°Cの温度範囲で1～数十秒の熱処理をするRTA (Rapid Thermal Annealing)技術でした。低抵抗化のため熱処理温度を上げると、不純物が拡散し、接合が深くなってしまいます。

この問題を解決するため、UX8ではMSA技術を適用しました。MSAは、1,200～1,300°Cの熱処理をミリ秒（1/1,000秒）で処理するアニール技術であり、不純物を拡散させずに、高い不純物活性化率を達成することができます。

図4は接合深さと不純物拡散層抵抗の関係を示したもので、MSAにより浅接合化と不純物高活性化による低抵抗化ができることが分かります。MSAの効果はトランジスタ特性に表れており、従来RTA技術に比べ、同じオフ電流I<sub>off</sub>で、高オン電流I<sub>on</sub>が得られています。

<sup>1</sup> 不純物とは、シリコン中に導入する電気的な活性元素のこと。N-typeでは砒素とリン、P-typeではボロンとインジウムが一般的。

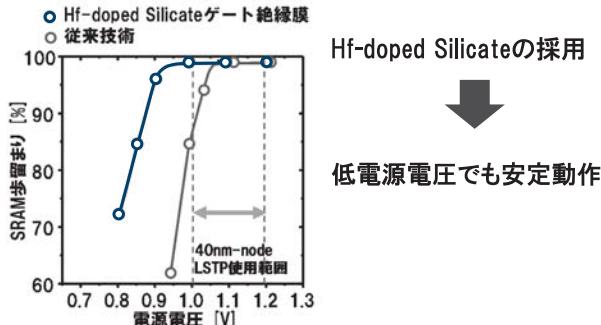

### 3.2 低電源電圧でも安定した回路動作を可能にする技術

#### —Hf-doped silicateの適用—

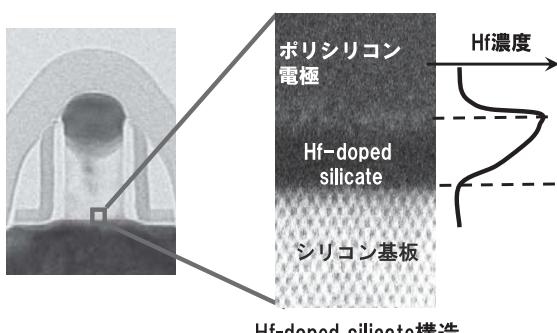

弊社では、UX7LSから、ゲート絶縁膜に、極微量のHf-doped silicateを適用し（図5）、チャネル不純物濃度を下げたトランジスタを使っています。

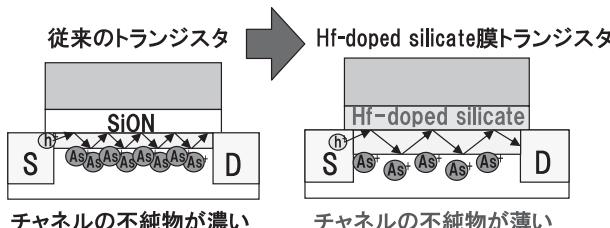

チャネル不純物濃度を下げるには、トランジスタの設計において3つの利点があります。1つ目は、ドレインー基板間リーキ電流が低減できること、2つ目は、チャネル不純物濃度が低下したことによる不純物散乱の影響が軽減し、移動度 $\mu_{eff}$ が向上すること（図6）です。

さらに、3つ目として、トランジスタ特性のランダムばらつきが減少することが挙げられます。

デバイスのスケーリングに伴い、トランジスタのチャネル領域内に存在する不純物原子は数えられるほど少なくなっています。近年、その不純物原子個数の統計的揺らぎによるトランジスタ特性のランダムばらつきが問題になっています。

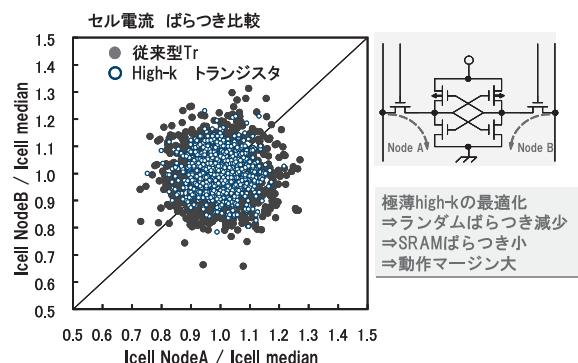

図7はSRAMのNode AとNode Bでの電流ばらつきを図示し

図5 トランジスタ断面TEM像とHf-doped silicate構造

チャネル不純物イオン( $As^+$ )の濃度が薄いので、ソース側から注入される電流(pFETの場合 正孔 $h^+$ )が散乱されにくいため、電流が流れやすくなる( $I_{on}$ 向上)。

図6 Hf-doped silicateを使用したトランジスタの利点

たものです。SRAMを構成するトランジスタのランダムばらつきにより、ノード間の相対関係がランダムになっていることが分かります。しかし、Hf-doped silicateを適用したデバイスでは、ランダムばらつきが小さくなっていることが分かります。

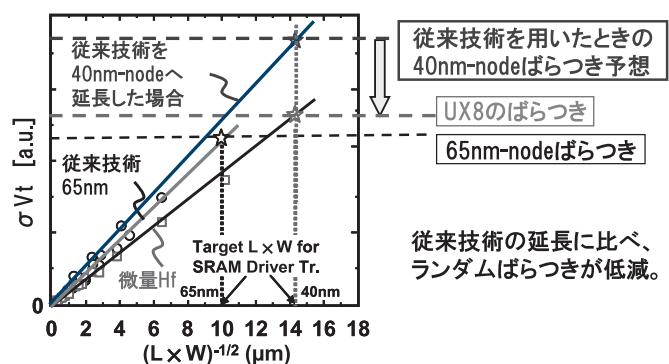

この不純物原子の個数揺らぎの影響は、トランジスタの大きさに依存し、 $1/\sqrt{LW}$ の比率（Lはゲート長、Wはゲート幅）で増加するため、スケーリングの阻害要因の1つでした。例えば1世代毎に、 $1/\sqrt{LW}=1/\sqrt{0.5}=1.4$ 倍とばらつきが増え、さらに1チップに搭載される素子数は単位面積当たりで2倍になり、ばらつき幅が単純に増加するので、回路設計の困難さを増大させます（図8の従来技術を40nm-nodeへ延長した場合の線）。NECエレクトロニクスではHf-doped silicateを適用したデバイス最適化によりランダムばらつきを抑えたので、スケーリングにより増大する回路設計への負担を軽減することができました（図8の微量Hfの線）。

図7 ランダムばらつき低減の効果

図8 トランジスタのサイズとランダムばらつき

図9 SRAM歩留まりの電源電圧依存

例えば、ランダムばらつきの低減効果はSRAM歩留まりに顕著に現れ、最低動作電圧を下げるることができました（図9）。

このように、Hf-doped silicateゲート絶縁膜は、トランジスタ性能の向上だけでなく、低電源電圧でも安定した回路動作を可能にしました。

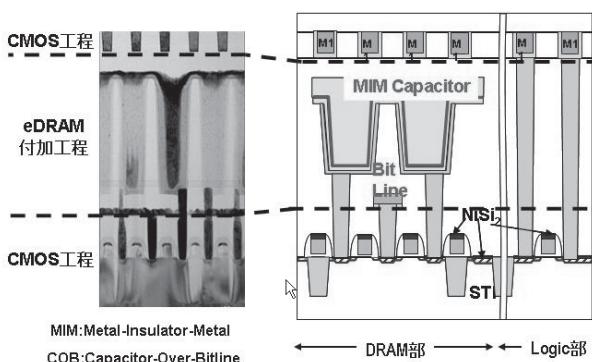

#### 4. UX8デバイスラインナップ

UX8では、アクティブパワーが低い0.9V系LOP (Low Operation Power) デバイスと、スタンバイパワーが低い1.1V系LSTP (Low Standby Power) デバイスの2種のコアデバイスを開発し、LSIの低消費電力化を求めるユーザー要望に合わせてコアデバイスの選択が可能なCMOSプラットフォームをつくりました。更に、開発当初よりDRAM混載前提の開発を進め、メモリ混載ロジックの先端製品にターゲットを合わせた

図10 DRAM混載logicプロセスのDRAM容量部断面構造

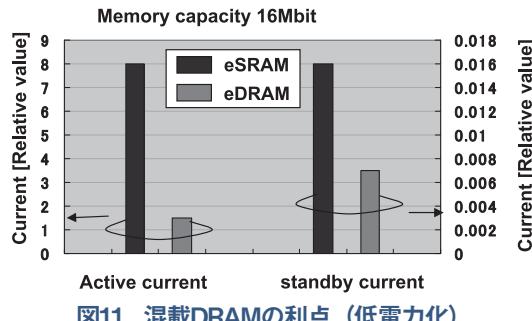

図11 混載DRAMの利点（低電力化）

プロセスを用意しました。図10は、メモリ混載ロジックにおけるDRAM部の断面図です。DRAM混載は、CMOS工程における下地工程と第1層配線工程の間に、メモリ容量を形成する工程の付加で製造できます。

混載DRAMの利点は、SRAMに比べて、セル面積が1/4になるだけでなく、図11に示したようにアクティブ電力とスタンバイ電力が大幅に低減します。混載DRAMは、大容量メモリを混載するSOCの低消費電力化に適しています。

#### 5. おわりに

前世代比2倍のゲート密度を実現する40nmノードCMOSプラットフォーム「UX8」を開発しました。UX8では、これまで培ってきた低消費電力対応デバイス技術をプラスアップし、最小限の新規技術追加で製造コストを抑え、高性能デバイスを実現しました。NECエレクトロニクスでは、UX8プロセスで幅広いアプリケーション領域において、低消費電力、高速化を実現するシステムLSIを提供します。

#### 執筆者プロフィール

深井 利憲

NECエレクトロニクス

先端デバイス開発部

基幹CMOS開発グループ

シニアプロセスエンジニア

高橋 寿史

NECエレクトロニクス

先端デバイス開発部

メモリデバイス開発グループ

チームマネージャー

池田 昌弘

NECエレクトロニクス

先端デバイス開発部

基幹CMOS開発グループ

シニアエキスパート

夏目 秀隆

NECエレクトロニクス

先端デバイス開発部

メモリデバイス開発グループ

チームマネージャー