# SX-9の実装技術

梅澤 和彦・浜口 博幸・武田 勉

保坂 忠男・名取 正樹・永田 哲也

## 要旨

本稿では、SX-9の実装技術の概要を述べます。SX-9ではシングルコアで世界最高性能を実現したCPUの性能を最大限に引き出すため、高密度LSI実装技術、高密度接続技術、高効率実装技術、高性能電源技術を駆使し、ノード当たり4Tバイト/秒という高いメモリバンド幅を実現し、優れたシステム実効性能を達成することができました。また、これらプロセッサ、システムの高い性能をアピールする先進的なデザインを採用しました。

## キーワード

●実装テクノロジ ●基板 ●実装 ●接続 ●筐体 ●電源 ●デザイン

## 1. まえがき

スーパーコンピュータSXシリーズの特徴は、すべてのCPUが1つのノード内においてすべてのメモリ空間を共有する点（共有メモリシステム）です。SX-9では共有メモリシステム全体を効率的に利用するため、LSIの高速動作、LSI間インターフェースの高速化に必要となる実装構造全般にわたる最適化を追求し、高密度、高効率実装を実現しました。これらを実現するために開発したSX-9の実装技術を以下に紹介します。

## 2. 高密度実装技術

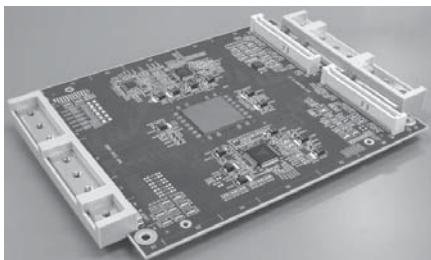

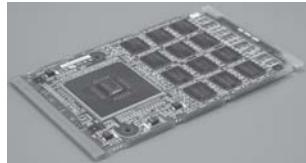

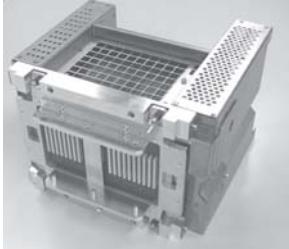

超高速動作が要求されるCPUパッケージ、及びRTRインターポーラー（以下RTR-IP）パッケージはSX-8にて採用した高密度実装を更に進化させ多ピンのLSIを搭載しています。CPUパッケージ、RTR-IPパッケージの外観を写真1、写真2に示します。CPUパッケージは、CPU LSIを大型ビルドアップ基板表面にペアチップ実装し、裏面には高密度多極コネクタを実装しています。RTR-IPパッケージはRTR LSIをセラミック基板表面に実装し、裏面にはRTRボードへ接続する

写真2 RTR-IPパッケージ

表1 CPU/RTR-IP/MMUモジュール諸元

| 項目       | CPU                             | RTR-IP                                                                            | MMUモジュール                                                      |                                                           |

|----------|---------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------|

| LSI(形態)  | CPU LSI × 1<br>(ペアチップ)          | RTR LSI × 1<br>(ペアチップ)                                                            | HUB LSI × 1 (BGA)<br>DRAM × 24 (BGA)                          |                                                           |

| ピン数/ピッチ  | 8960/168 μm                     | 6093/168 μm                                                                       | 840/1.0mm                                                     |                                                           |

| サイズ(mm)  | 19.84 × 21.04                   | 15.98 × 15.98                                                                     | 31 × 31 ※HUB LSI                                              |                                                           |

| 配線基板     | 種類<br>サイズ(mm)<br>層数<br>配線密度(μm) | ビルドアップ<br>プリント配線基板<br>140(W) × 112.5(D) × 1.6(t)<br>4ビルド-8コア-4ビルド<br>配線幅/間隙=18/18 | セラミック<br>積層基板<br>50(W) × 50(D) × 3.4(t)<br>35<br>配線幅/間隙=66/60 | プリント配線基板<br>65(W) × 135(D) × 1.6(t)<br>12<br>配線幅/間隙=80/80 |

| パッケージ端子数 | 2,628                           | 3,600                                                                             | 170                                                           |                                                           |

ためのはんだボールが形成されています。このRTR-IPパッケージとMMUモジュールはマザーカードとなるRTRモジュールに実装されます。CPUパッケージ、RTR-IPパッケージとMMUモジュールの諸元を表1に示します。

写真1 CPUパッケージ

### 2.1 LSI実装技術

LSIの性能を最大限に引き出すために、SX-8から、更に高密度化したペアチップ実装を採用しています。CPU LSIは微細ビルドアップ配線基板に、RTR LSIはセラミック配線基板に鉛フリーはんだで接続されています。そして、LSIと配線基

表2 RTRモジュール基板の諸元

| 項目       | RTRモジュール基板                        |

|----------|-----------------------------------|

| サイズ(mm)  | 310(W)×294(D)×4.5(t)              |

| 材料       | 低誘電正接材                            |

| 層数       | 28(うち信号層9)                        |

| 配線密度     | 2本/0.8mm                          |

| 配線仕様(μm) | 配線幅/間隙=65/70                      |

| 実装デバイス   | CPUコネクタ×17, RTR-IP×2, MMUモジュール×32 |

板間の接続信頼性確保のため、アンダーフィル樹脂を充填しています。狭ピッチはんだ形成、搭載、樹脂充填といった製造技術の向上により、SX-8より接続端子数の増大並びに狭ピッチ化を実現しています。

## 2.2 配線基板技術

### 1) 微細ビルドアップ配線基板

CPUパッケージで採用したビルドアップ基板はアディティブ工法によるパターン形成、レーザー工法によるヴィア形成により、配線ピッチ36 $\mu$ m(配線幅/間隙=18/18 $\mu$ m)という微細化を実現しています。また、ビルドアップ層を表裏各4層形成することで8,000を超えるペアチップのIO端子を受け、全信号を引き出しています。

### 2) 高多層プリント配線基板

RTRモジュール基板は、電気特性のすぐれた最先端材料(比誘電率:3.7、誘電正接:0.002)を採用した高多層プリント配線基板です。各部品を高密度に配置することで配線長を抑制し、更に高周波信号伝送のため、各部品のパッド形状の最適化やスルーホール容量を低減した構造の採用、銅箔表面の凹凸を抑えたロープロファイル銅箔を採用しました。また、搭載部品のピンアサインを最適化し、0.8mmピッチのスルーホール間を配線幅/間隙=65/70 $\mu$ mで通すことで配線収容性を向上させています。諸元を表2に示します。

## 3. システム実装技術

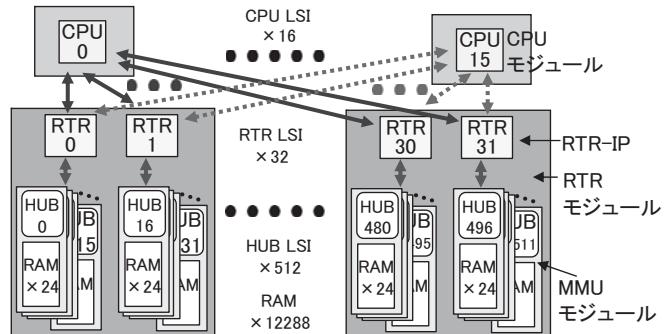

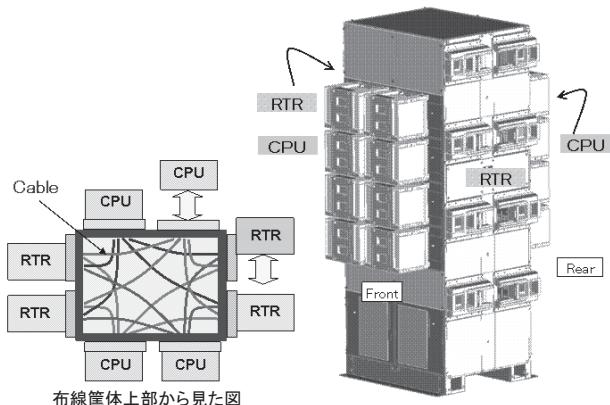

システム構成図を図1に示します。すべてのCPUがRTRを介して全MMUと接続される共有メモリ構成となっています。この共有メモリを構成する各モジュールを効率的に接続するため図2に示すような4面実装方式を採用しています。本方式

図1 SX-9のシステム構成図(実装階層図)

図2 実装構造図

では、ケーブルを収容した布線筐体の前後面にCPUモジュールを16台、左右側面にRTRモジュールを16台配置し、各モジュールを256本に及ぶ高周波多芯ケーブルで直接接続することで各LSI間の超高速インターフェースを実現し、ノード当たり1.6TFLOPS、1Tバイト共有メモリ構造を実現しています。またRTRモジュールをCPUモジュールと同一方向で保守可能とすることで、4面実装でありながら2面保守を実現しています。

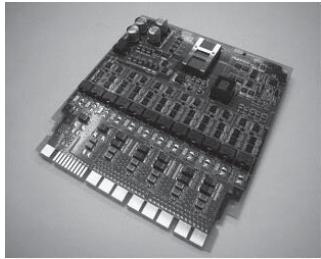

## 3.1 CPU/MMU/RTRモジュール実装

CPU/MMU/RTRモジュールの外観を写真3、写真4に示します。CPUモジュールにはCPUパッケージ、光モジュール、DC-DCコンバータが搭載されており、裏面にケーブル接続用コネクタが搭載されています。MMUモジュールには、HUB LSIとRAMが搭載されます。また、RTRモジュールには、RTR IP、MMUモジュールなどが搭載されており、裏面に

写真3 CPUモジュールとMMUモジュール

写真4 RTRモジュール

ケーブル接続用コネクタが搭載されています。

### 3.2 接続技術

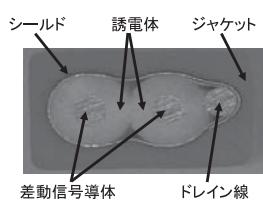

CPU-RTRモジュール間の高速インターフェースを実現するために高周波多芯ケーブルと駆動メカを開発しました（写真5）。

#### (1) 高周波多芯ケーブル

高密度かつ高周波伝送を実現するために、誘電体にEPTFEを採用したサイドドレインタイプの微細Twinaxケーブルを採用しています。これによりコントラクトピッチは0.5mmとなり、PWB上の占有面積225mm<sup>2</sup>内に差動信号48ch（146ピン）が収容可能となり、高密度接続を実現しています。

#### (2) 駆動メカ（ケーブル挿抜機構）

1ノード当たり約600箇所（CPUモジュール当たり18本、

写真5 高周波多芯ケーブルと線材断面

RTRモジュール当たり17本）のケーブル接続を効率よく行うために駆動メカによる接続を採用しています。これは、過去のSXシリーズにて培ってきた技術であり、一操作をすることで複数本のケーブルを一度に接続するものです。

### 4. 壁体技術

SX-9シリーズでは、性能を重視した壁体構造を採用しました。モジュール間を接続するケーブルはCPU壁体中心部の布線壁体の中にルーティングし、その周囲にCPUモジュール、及びRTRモジュールを効率よく実装することで高密度化を実現しています。しかしながら、発熱源となるユニットを集中することとなったため、これらを効率よく冷却することが大きな課題となりました。この課題に対しては、シミュレーション並びに実機評価にて各部品の発熱量に応じた風の分配、流れを最適化することにより、冷却効率を向上させ、特殊な付帯設備を使用することなく一般的なマシン室への設置容易化を図っています。

### 5. 電源技術

SX-9の設置面積、消費電力を改善するために、電源システムにおいて、高密度実装による小型化と高効率化を実現しています。AC200~240VをAC-DCコンバータで受電し、DC48VをDC-DCコンバータに分配するDC48V給電方式を採用しています。フロントエンドのAC-DCコンバータは複数台で並列運転しており、システム構成規模に応じた電力を供給します。更にAC-DCコンバータ故障時でもシステム運用が可能なようN+1冗長構成により信頼性を確保しています。また、AC二重化受電を行い、信頼性を高めています。DC-DCコンバータはDC48VをDC1.0V~3.3Vに変換し、電力供給しています。1.0Vの低電圧において200A近くの大電流を供給するため、給電系の電圧ドロップ、負荷変動による電圧変動を抑える必要があり、DC-DCコンバータをCPUモジュールやRTRモジュールに直接バス接続あるいはコネクタ接続することにより、給電インピーダンス、給電インダクタンス成分を抑えていました。SX-9で開発したDC-DCコンバータの外観を写真6に示します。入力電圧DC48V、出力電圧DC1.0V~3.3V、出力電流は最大260Aを実現しました。基板は140mm×150mm、部品高さは約20mm、実装密度620A/リットルであり、前機種SX-8比1.7

写真6 DC-DCコンバータ

倍の実装密度となっています。電力効率は85%peakと低電圧大電流DC-DCコンバータとしては高い効率を達成しています。

## 6. デザイン

スーパーコンピュータSXシリーズにおいてはこれまで、Evolution & Innovation (進化 & 革新) を常にテーマの中心に据えてデザインを行ってきました。

今回、SX-9のデザインにおいてはこのメインテーマに沿った形で、3つの大きなデザイン的挑戦によって新しいスーパーコンピュータのイメージを表現しています（写真7）。

### (1)スマートで先進的なフォルム

SX-9の複雑な曲線を描くエンドカバー形状は、板金とモールドのハイブリッド構成により作り出されました。特にそのフレームには先進のプレス加工技術を用いることで、美しさと加工性を両立させています。また、全体の造形はこのエンドパネルを目立たせるために、あえてシンプルにまとめました。

### (2)高輝度発光LEDを使用した透過光ロゴデザイン

エンドカバーのSX-9ロゴの“X”には透過照明文字を使用

写真7 スーパーコンピュータSX-9の全体像

し、装置デザインのシンボル的な意味合いを持たせました。さらにこのロゴは数秒ごとに緩やかに明滅することで、これまでのSXシリーズの静的なデザインから脱却、空間軸に加え時間軸を持つアクティブライメージのデザインとなりました。

### (3)高品質なグロスフィニッシュ黒色塗装

SX-9の全体塗装にはその価値にふさわしい、黒曜石のような美しい艶を持った黒色塗装を施しています。これまで、これほどのサイズの光沢塗装は、大きな量産設備をもつ自動車業界などごく限られた業種にのみ可能でしたが、今回、塗装工場にクリーンルームの設置を仰ぐなど、様々な検討や努力を行うことで初めて実現可能となりました。

これら、スタイリング上の処理に加え、フレキシブルなレイアウトに対する対処など、様々な条件をクリアすることで、SX-9のデザインは高い次元でバランスの取れた完成度の高いデザインとなっています。

## 7. むすび

以上、SX-9の実装技術とデザインについて紹介しました。なお、SX-9は、NECが定めた環境配慮基準、及びグリーン購入法に適合した環境配慮型コンピュータとなっていることも特徴です。これからも高い性能と信頼性を備え、コストパフォーマンスに優れたスーパーコンピュータを開発し社会に貢献することがNECに課せられた使命と考えています。今後も、実装技術力向上に努め、魅力ある製品の開発に貢献していく所存です。

## 執筆者プロフィール

梅澤 和彦

第一コンピュータ事業本部

コンピュータ事業部

統括マネージャー

武田 勉

第一コンピュータ事業本部

コンピュータ事業部

主任

名取 正樹

NECコンピュータテクノ

コンピュータ共通技術部

エキスパート

浜口 博幸

第一コンピュータ事業本部

コンピュータ事業部

マネージャー

保坂 忠男

NECコンピュータテクノ

コンピュータ共通技術部

エキスパート

永田 哲也

NECデザイン

プロダクトデザイン2部

エキスパートデザイナー