# 小型/薄型プロードライザ

源新輝

**要旨**

プロードライザは、ギガヘルツ帯までの広い周波数帯域でノイズを吸収とともに、素早く電流を供給し、電源ラインを安定化させるデカップリングデバイスです。本稿では、ゲーム機、ノートPCなどで採用され、昨年のNEC技報でご紹介したFケース（16.7mm×12.1mm×2.5mm）<sup>1)</sup>をダウンサイジングした、小型/薄型の新製品であるDケース（9.5mm×5.5mm×2.0mm）の製品紹介を主体に、ネットワーク機器、放送機器などに採用され始めているFPGA（Field programmable gate array）を搭載したテストボードの評価例を紹介します。

**キーワード**

●小型 ●薄型 ●ノイズ対策 ●伝送線路 ●電源分離

## 1. まえがき

近年のエレクトロニクス市場における技術動向は、半導体のマルチコア化が進展し、低電圧化、高周波化が進んでいます。一方、コンデンサなどの受動部品に関しても、半導体の技術動向に伴い、小型化、高機能化、および部品点数の削減が急務であるといえます。

このような背景のなか、当社では広い周波数帯域において低インピーダンス、大容量という特徴を有し、優れたデカップリング機能とノイズ対策機能を併せ持つ新デカップリングデバイス、プロードライザの量産に成功しました。

本稿では、本格的に量産が始まったプロードライザの概要、およびさらなる市場拡大へ期待される小型/薄型プロードライザについて説明します。

## 2. プロードライザの概要

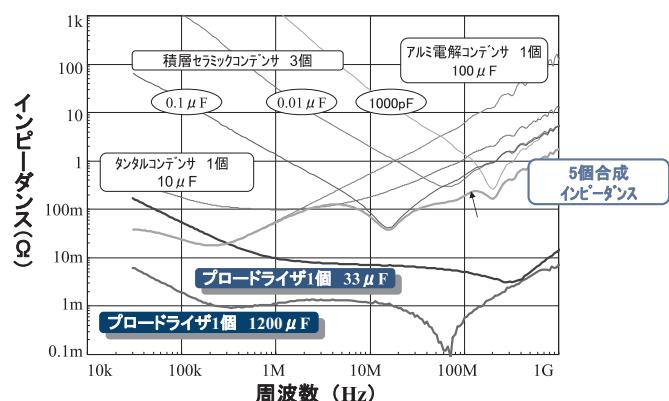

プロードライザは、陽極にアルミ、陰極に導電性高分子を使用しながら、高周波において一般的な技術であるストリップライン構造を形成することにより、図1にあるように、広い周波数帯域にわたって、低インピーダンスであるという特徴を有しています。

プロードライザには、すでにゲーム機やノートPCで採用されているFケースがありますが、NECトーキンでは低ESR化など、さらなる特性向上をめざして開発を進めています。

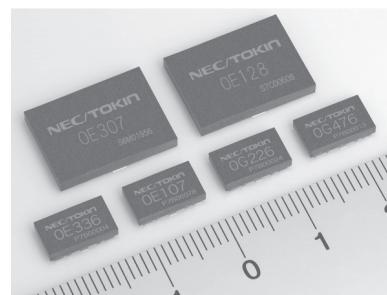

また、形状においても同様に基板などの小型化/員数削減など、お客様の設計思想にマッチするよう、小型/薄型であるD

ケースをラインナップしました（表）。面積比で約26%まで縮小してもなお、フラットで低インピーダンスである特性はそのまま維持することを可能としました。Dケースの製品外観を写真の下段に示します。

図1 プロードライザ インピーダンスの周波数特性

写真 プロードライザの製品写真（下段：Dケース）

## ノイズ&パワーデバイス 小型/薄型プロードライザ

表 Dケースラインナップ

| 型番           | 形状(mm)      | 定格電圧(V) | 静電容量(μF) |

|--------------|-------------|---------|----------|

| PFAD200E336M | 9.5×5.5×2.0 | 2.5     | 33       |

| PFAD200E107M | 9.5×5.5×2.0 | 2.5     | 100      |

| PFAD200G226M | 9.5×5.5×2.0 | 4.0     | 22       |

| PFAD200G476M | 9.5×5.5×2.0 | 4.0     | 47       |

### 3. プロードライザの特徴

プロードライザは、フラットな低インピーダンスを実現するために、内部素子ではストリップライン（伝送線路）構造を形成しています。この構造は通常、同軸ケーブルや、高周波基板のパターン設計に用いられます。この技術をキャパシタに取り入れ、具現化したものがプロードライザです。

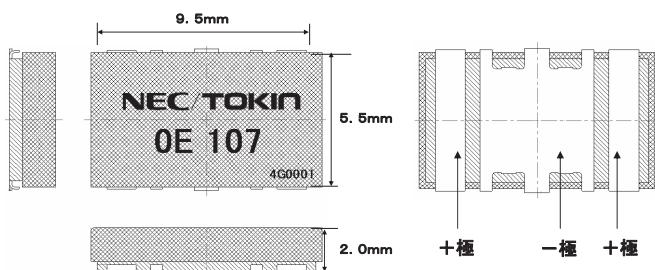

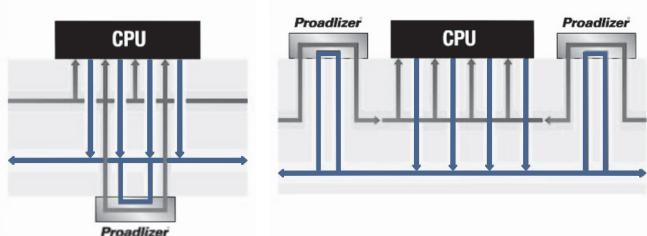

その構造がゆえ、図2のように、両側に陽極端子が1つずつ、中央に陰極端子を有しています。プロードライザを用いる場合、設計方法としては、両側の陽極を内層の同じ電源プレーンに、陰極を同じGNDプレーンに接続する一般的な設計「キャパシタデザイン」（図3-1）、もしくは両側の陽極を

図2 外観

図3-1 キャパシタデザイン

図3-2 フィルタリングデザイン

図3 プロードライザの設計方法

別々の電源プレーンに接続する、電源分離設計「フィルタリングデザイン」（図3-2）の2通りが考えられます。

### 4. FPGA搭載ボードによる電源分離効果

FPGAは、フレキシブルにカスタマイズができるゲートアレイとして、ASICの試作段階や生産台数が少量の製品で使用されてきましたが、性能の向上とコストの低減により、近年、携帯電話の基地局を中心に各種ネットワーク機器や放送機器、デジタル家電の制御部にまで採用されています。

今後、ますます、高性能化、大規模化が進展するFPGAにおいても、電源の低電圧化、ノイズ低減に対する考慮は必須であり、電源部の回路設計は非常に重要となっています。

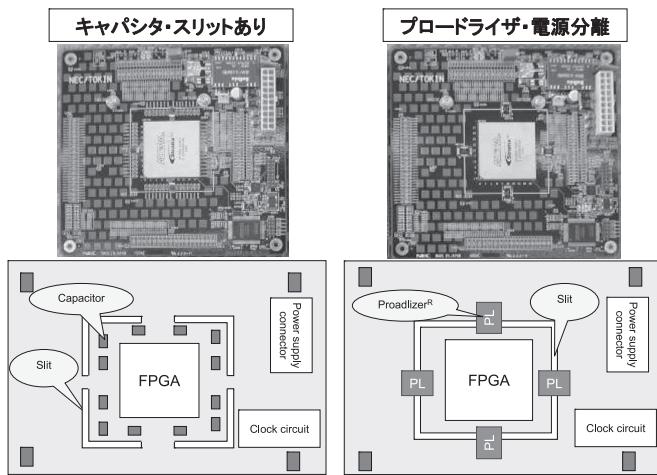

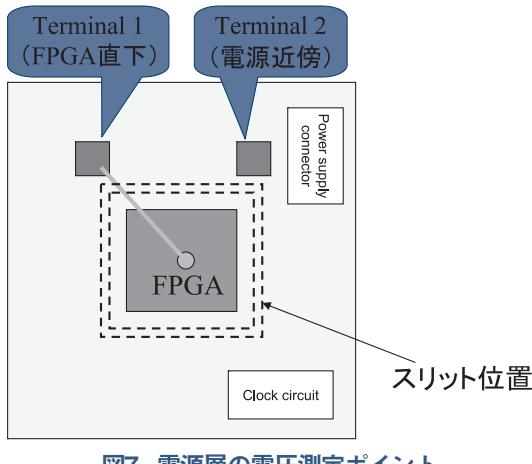

ここでは、プロードライザと電源分離設計の効果を確認する回路として、FPGA搭載ボードを試作しました。条件としては、プロードライザと従来キャパシタ、電源分離有無の組合せにより、2種類のボードで比較します。電源分離設計は、電源層において、FPGAの周囲にスリットを入れ、FPGA側と電源側を分離し、FPGAのノイズをFPGA近傍に閉じ込め、周囲へのノイズ抑制効果を高めることを期待しています。プロードライザは、開発当初の15μF品を4個使用し、FPGA周囲のスリット一辺に1個配置し、プロードライザを通して電源を供給しています。従来のキャパシタは、10μF品：1個、1μF品：4個、0.1μF品：10個を用い、プロードライザと静電容量を同一にしてスリット一辺に1セット配置しました。キャパシタでは電源を通過させることは不可能なので、従来の2端子キャパシタを使用したボードのスリットは、プロードライザを搭載する位置に相当する部分のスリットをなくし、電源層を通して電源を供給する設計としました。そのFPGA搭載ボードの外観とイメージを図4に示します。

ここで使用するFPGA搭載ボードの構成内容としては、FPGAの電源ラインに所要電流の変動を発生させ、電源電圧の変動やEMIを評価するために、ソフトウェアによりFPGA内部に多数のレジスタを構成しました。FPGA内部のレジスタRegを反転しながら接続し、1個おきのレジスタから出力を外部に引き出して外部のキャパシタに接続します。これにより、外部のキャパシタには、同じ出力が出力され、FPGAの電源には、大きな同時動作ノイズが発生させることができます。

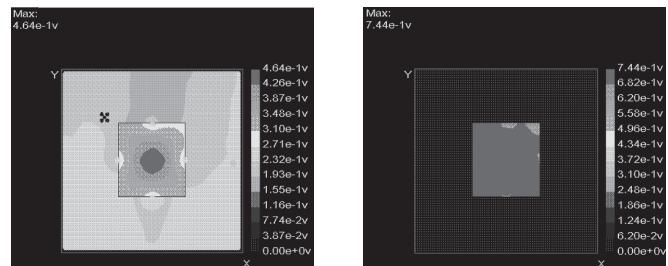

FPGA搭載ボードを実際に評価する前に、本ボードの設計データを用いて、電磁界シミュレーションにより、電解分布

図4 FPGA搭載ボード 外観とイメージ図

について事前に検討しました。シミュレータは、部品の実装されたプリント基板について信号/グラウンド間のリターン電圧・電流や電源/グラウンド間のプレーン間電圧・電流を計算でき、システムのデカップリング設計やEMI解析などに応用できる米国Sigriity社のSPEED2000を使用しました。

FPGAの電源電流変動モデルとしては、FPGAの電源ライン位置に150MHz、16Aの三角波電流減を接続し、さらに、プロードライザ、従来キャパシタのスパイクモデルをそれぞれプリント配線基板の所定位置に接続しました。以上の設定により、シミュレーションを実行し、各ボードの電源層における電界分布を求めた結果を図5に示します。この結果から、電源層をスリットで分離したボードは、FPGAのあるスリット内側に高周波電流が集中していることが分かります。特にプロードライザを使用したボード（図5-2）は、プロードライザの低インピーダンスな特性とスリットによる分離設計のため、高周波電流を閉じ込める効果が非常に大きい結果となっています。従来キャパシタを使用したボード（図5-1）は、スリットに切れ目があるために、一部高周波電流が切れ目から漏洩して、電圧変動がボード全体に拡散しており、スリットの効果が充分に活かしきれていない結果となっています。

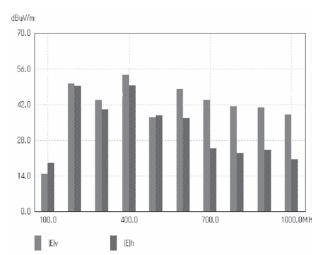

さらに、本ボードから放射される放射ノイズをシミュレーションにより求めた結果も図6に併せて示します。一般的にボードから放射される放射ノイズは、高周波電流が広く分布しているほど大きくなる傾向がありますが、シミュレーションの結果も、先の電界分布を反映して、電圧変動の最も少な

図5-1 キャパシタ・スリットあり

図5-2 プロードライザ・電源分離

図5 電解分布シミュレーション結果

図6-1 キャパシタ・スリットあり

図6-2 プロードライザ・電源分離

図6 EMIシミュレーション結果

かったスリットを設けたプロードライザのボード（図6-2）が、放射ノイズも小さいという結果が得られました。

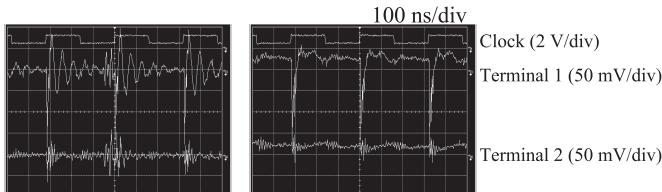

次に、実際にボードを動作させて、電源ラインに重畠するノイズの測定を行いました。ボードに設けた測定用ターミナル1、2にプローブをあてて、オシロスコープにより電圧に重畠するノイズを測定しました。ターミナル1は内層を通してFPGA中央付近のコア電圧を引き出し、ターミナル2はオンボード電源の出力に近いポイントに設けました。測定ポイントの位置を図7に、電源のノイズの測定結果を図8に示します。それぞれのノイズ波形観測結果における上段の波形は、クロック波形、中段がターミナル1、下段がターミナル2で測定したノイズ波形です。各ボードに共通して、クロックの立ち上りに同期して電源ラインにノイズが発生し、ターミナル1のFPGA直下におけるノイズの方がターミナル2のオンボード電源出力部に近いポイントのノイズよりも大きいことが分かります。ボード間の比較では、電源分離設計とプロードライザを組み合わせたボードが他のボードよりノイズが小さく、良好な結果が得られました。

## ノイズ&パワーデバイス 小型/薄型プロードライザ

図7 電源層の電圧測定ポイント

図8-1

キャパシタ・スリットあり

図8-2

プロードライザ・電源分離

図8 ノイズ測定結果

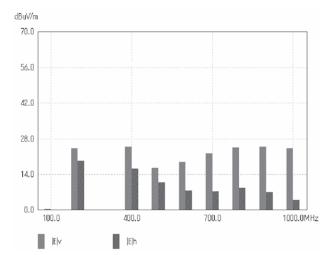

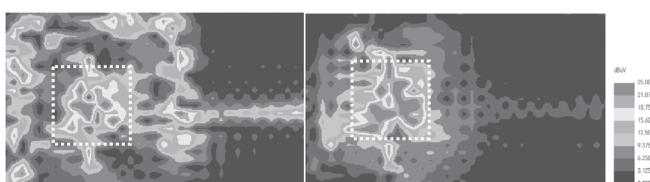

次に、実測として近傍磁界を測定しました。それぞれのFPGA搭載ボードを、プリント基板用電磁波測定装置のテーブルの上に設置・駆動し、細かくメッシュ状に区分けした各エリアごとにスキャンし、そのノイズレベルを測定します。

キャパシタで構成されたボードは、そのボード全体にノイズの観測点が見られます。一方、プロードライザで電源分離設計を用いたボードは、電源分離するために設けたスリットのなかにだけノイズの観測点が存在し、その外側周囲にはほとんどノイズが見当たらないという結果になっています。

図9-1

キャパシタ・スリットあり

図9-2

プロードライザ・電源分離

図9 近傍磁界測定結果

この近傍磁界実測の結果（図9）は、先のシミュレーションの電解分布結果（図5）と比較すると、非常に酷似しているのが分かります。このように、実機により様々な評価検証をするのはもとより、シミュレーションによる概略の傾向を事前検証できることを実証できました。

### 5. 電源分離効果の有効性

第4章では、プロードライザによる電源分離の効果について述べてきました。実際、この設計方法が効果を発揮できる主な市場としては、携帯電話の基地局向けメインボード、および通信機器などのネットワーク市場、省スペースかつ多機能型セットを扱う市場などが考えられます。

このような、ノイズ・EMI対策設計を強いられている市場に対し、従来の設計思想で対策するためには様々な問題をクリアする必要があります。複数の積層セラミックキャパシタを使用することで発生する反共振対策、それに伴う員数増加、スペース拡大など、このような状況に対しプロードライザは、電源分離設計をすることにより、基板設計の段階で対策を施すことが可能であることに優位性があると考えています。

### 6. まとめ

近年の技術動向は、半導体の多様化、高速化に伴い、周辺部品に対する要求も高まりつつある状況です。このようなトレンドに対し、プロードライザは、広帯域での低インピーダンス特性や、電源分離によるノイズ対策など、様々な側面より優位性がある製品です。今後は、さらなるシリーズ拡大や低コスト化を進め、お客様に貢献したいと考えています。

#### 参考文献

- 1) 高橋健一ほか：「新デカッピングデバイス「プロードライザ」の開発、量産」、NEC技報、Vol.59, No.5, pp/50-55, 2006年11月

- 2) 堀仁孝ほか：「電源雑音除去の新手法を学ぶ(2)」、日経エレクトロニクス、2006.12.4

#### 執筆者プロフィール

源新輝

NECトーキン

ソリューション技術部