# Hybridエミュレータによるプロセッサ設計検証

山田一男・西本浩秋

大東正行・小野洋彦

## 要旨

近年、FPGAベースとしたプロトタイピングボードを使い、実チップの完成前にシステム検証を行う手法の適用が広がっています。今回、NECエレクトロニクスのV850E1後継の次世代プロセッサの検証に、NECのシステムIPコア研究所で開発されたプロトタイプボードHybridエミュレータを適用し、実チップの完成数ヵ月前にインサーキットエミュレータ(IE)検証をスタートすることができました。さらに、Hybridエミュレータの持つカスタムデバッガを用いて、IE検証に先んじて、システム検証、SWベンチマークを実行する環境を構築し、顧客ベンチマーク測定によるプロモーション活動や、コンパイラ改善の評価に用いて、その検証を前倒しする効果を上げています。Hybridエミュレータのプロセッサ検証への適用を紹介します。

## キーワード

- エミュレータ

- 協調検証

- プロセッサ開発

- 評価プロセス

- インサーキットエミュレータ

- 事前検証

- 性能評価

- 開発ツール

- カスタムデバッガ

## 1. はじめに

プロセッサLSIの開発では、LSI自身の開発期間短縮だけでなく、インサーキットエミュレータ(IE)、コンパイラ、OSなどの開発環境の整備期間の短縮も重要となります。

今回、V850E1後継の次世代プロセッサ開発では、IE検証の前倒しによる設計期間の短縮を目的として、NECのシステムIPコア研究所で開発されたFPGAベースプロトタイピングボードHybridエミュレータを、マイコンの評価プロセスとして初めて導入しました。

## 2. マイコンの評価プロセスとHybridエミュレータ導入目的

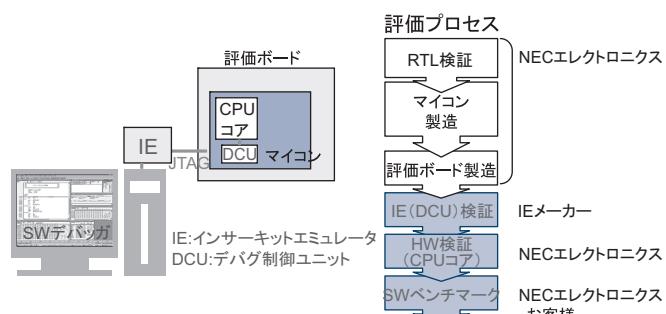

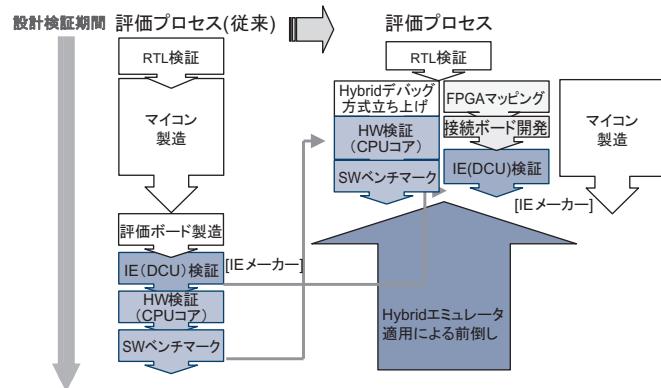

マイコンの評価プロセスは、図1のようになっています。レジスタトランスマスファーレベル(RTL)の回路検証の後、マイコン製造および評価ボード製造を行い、サンプルチップを使用してインサーキットエミュレータ(IE)の開発を行います。

IEは、シリアル通信規格であるJTAGのバウンダリスキャン機能を利用して、CPU内にあるデバッガ制御ユニット(DCU)にアクセスし、CPU上でのプログラム実行、ブレーク、モニタなどの機能を提供するものです。

実チップの制御並びにデバッガは、このIE機能を用いて行

うため、IEの動作を確認し、その後、HW検証、SWベンチマークという順序で評価を進める必要があります。

次世代プロセッサは、IEとCPUのデバッガプロトコルが、従来と異なるNEXUS標準プロトコルに対応しており、検証の対象となりました。

IE検証は実チップが完成した後に、IEボードを立ち上げる従来の方法に対し、FPGAに回路をマッピングし、IE検証を実チップ完成前に前倒しするというのが、今回のFPGAベースとしたプロトタイピングボード導入の目的です。

さらに、もう1つの目的は、IEインターフェースを用いずに、Hybridエミュレータの持つカスタムデバッガの機能を使い、で

図1 従来のマイコン評価プロセス

## 先端製品を支える共通技術・基盤技術 Hybridエミュレータによるプロセッサ設計検証

きるだけ早期にSW検証および、プロセッサ性能ベンチマークを行い、システム動作を確認することです。

### 3. Hybridエミュレータの機能

#### 3.1 概要

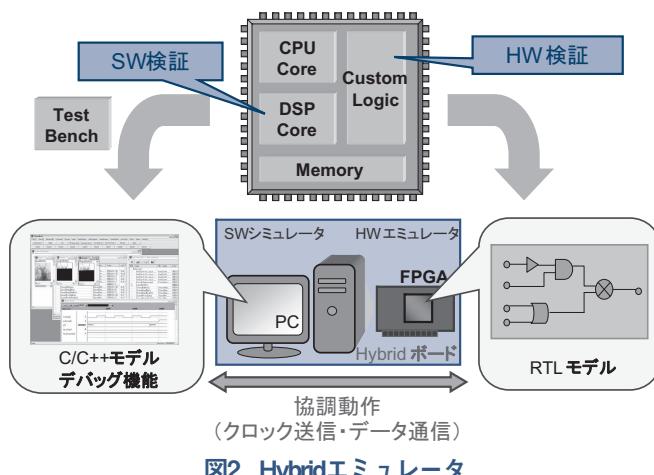

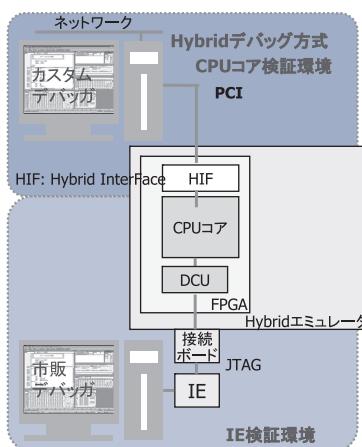

Hybridエミュレータは、図2のようにFPGAを搭載したHybridボードと、PC上のSWシミュレータ（ClassMate）から構成されます。

クロック送信とデータ通信の管理機構により、FPGAを搭載したHybridボードと、PC上のSWシミュレータ上のデバッグ機能の協調動作を実現しています。

一般的なFPGAベースのプロトタイプボードにないHybridエミュレータの特徴としては、以下の特徴1、2の部品（ライブラリ）を持ち、回路構造に合わせて組み合わせ、回路の制御、モニタリングを含めたデバッグ環境を短期間で構築する柔軟性を提供している点です。プロセッサなどに搭載される専用のデバッグ制御ユニット(DCU)に比べ、デバッグ機能は基本的なものですが、DCUでカバーされない特性の観測をカスタマイズして提供できる点が、従来のIEベースの検証環境では実現できなかったメリットです。

図2 Hybridエミュレータ

#### 3.2 特徴1：HW制御用基本ブロックライブラリ

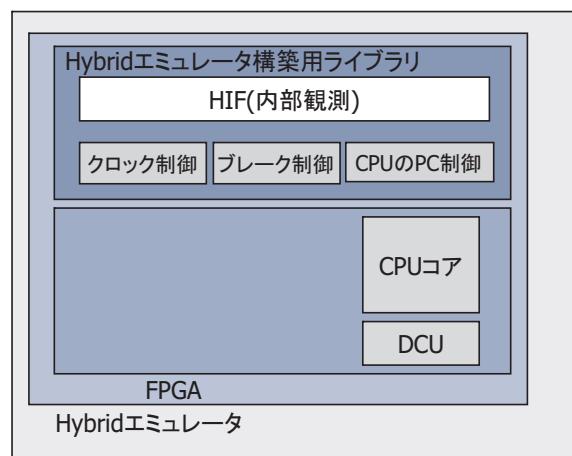

ボード上のクロックで高速にHWをエミュレートしながら、HW側のブレーク条件設定や実行制御を可能にするために基本ブロックとして、以下のライブラリを提供しています(図3)。

##### (1) クロック制御ブロック

分周クロックも含めたクロック生成を制御します。

##### (2) ブレーク制御ブロック

実行を一時停止するためのブレーク条件の設定・管理を行います。

##### (3) プログラムカウンタ(PC)制御ブロック

FPGA側にCPUを実装した場合に、SWデバッガで検証SWの実行管理を行います。

これらの基本制御ブロックは、特徴2のカスタムデバッグルイブラリから設定を可能とするインターフェースを有し、SWデバッガ上でのブレーク設定などと連携し、回路の実行時の制御を行います。これにより、FPGA上、MHzオーダーの高速実行しながら、PC側からのSWのデバッガや、性能評価を可能としています。

#### 3.3 特徴2：カスタムデバッグルイブラリ

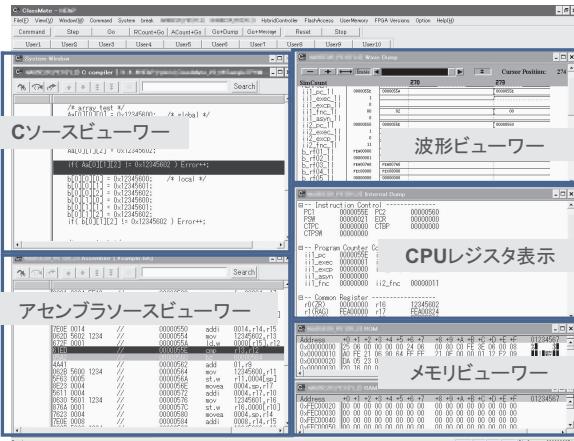

Hybridエミュレータは、サイクルベースの弊社製SWシミュレータ（ClassMate）の提供する様々なGUIベースのカスタムデバッグルイブラリを利用しています（図4参照）。

図3 Hybridエミュレータ構築用ライブラリ

図4 ClassMateが提供する様々なデバッグビューアー

#### (1) Cソース、アセンブラソースビューアー

SWデバッグのためのCソース、アセンブラのソースラインデバッグ機能を提供します。GUIのソースライン上、ブレーク設定やステップ実行などの制御が可能です。

#### (2) 波形ビューアー、CPUレジスタ表示、メモリビューアー

HW・SW検証に必要となるメモリビューアー、HW信号波形ビューアーなどのデバッグ機能を提供します。HWのレジスタをカスタムデバッガから設定することにより、FPGAへの実装をし直さなくてもHW構成を変更したプロトタイプ検証が可能となります。

### 4. IEによるプロトコル検証(IE検証)

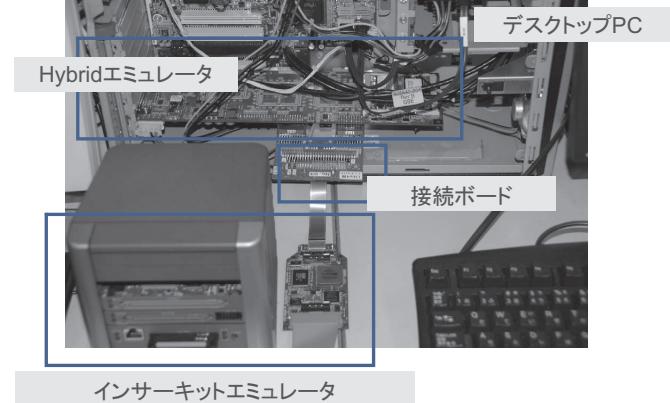

今回の1番目の目的である、IEによるプロトコル検証では、HybridエミュレータのFPGAボードの機能を主として用い、図5のように接続ボードを介して、IEに接続した環境を構築しました。

検証の内容としては、NEXUS標準プロトコルの正常通信、IEからのCPUの実行制御、トレース、モニタ機能などCPU依存部分の機能確認検証を行っています。

IEと通信を行うDCUの内部信号をClassMate側のデバッグビューアーに引き出すことにより、実チップでは困難なDCU内部信号を観測しながらのIE検証が可能となりました。実IE環境との接続では、タイミングが原因で期待した動作が得られないという問題も、この機能を使い問題の特定を行い、早

図5 インサーキットエミュレータによるプロトコル検証

期に解決されています。

また、IE環境を立ち上げ、検証を前倒しした効果として、シリコン製造前にRTLの不具合が発見され、リスピンを未然に防ぐことができました。

### 5. SW開発環境およびプロセッサ性能ベンチマーク

IE検証では、接続ボードを含めた環境の開発立ち上げに、数ヵ月を要しましたが、その立ち上げ作業とは並行して、導入の2番目の目的であるHybridエミュレータのカスタムデバッゲ環境 (Hybridデバッグ方式) の構築を行いました。

構築では、HW制御用基本ライブラリとカスタムデバッグルイブラリを今回の次世代プロセッサのハードウェアの構造に合わせて組み合わせ、その特徴に合わせて、SWデバッガの表示の改良や必要となるモニタ信号の引き出しを行っています。基本ライブラリの整備により、IE検証がスタートする前に、アセンブラ、コンパイラなどのSW開発環境が立ち上がり、新しいCPUでの性能も早期に測定可能となりました。この環境は、予定通りの機能・性能を持っているかを、事前に確認する手段となりました。

この立ち上げにより、サンプル出荷前の早い段階からマイコン商談先のお客様のSW性能ベンチマークにも利用することができました。特に、現在車載向けプロセッサではSWの計算精度 (実行サイクル数) が重要になってきていますが、実チップと同一のサイクル精度でSWベンチマークを事前に実施できることは、設計品質の向上だけでなくマイコン商談を牽引するための情報の提供が可能になります。

## 先端製品を支える共通技術・基盤技術 Hybridエミュレータによるプロセッサ設計検証

さらに、マイコンの商品企画を検討する上でも、実機と同じ精度のプロトタイプが用意できることにより、精度の高い性能評価が行えます。さらに、詳細な仕様・性能を実機と同じ精度で確認でき、お客様からの問合せに精度の高い回答ができるようになります。

### 6. マイコン評価プロセスの改善

プロセッサ設計検証環境へのHybridエミュレータ適用により、IEの設計・製造・検証と、SWベンチマーク、およびHW・SW協調検証を並行して実施することが可能となり（図6）、マイコン評価プロセスは、図7のように従来と比較して数ヵ月前倒しすることができました。

### 7. 今後の展開：プロセッサ検証環境のプラットフォーム化

製品・用途ごとにプロセッサ検証環境を構築する方法では、各々立ち上げ期間が掛かるため、タイムリーに製品展開がしづらい問題があります。

その対策として、検証環境立ち上げを効率化するために、プロセッサ+周辺マクロの検証プロトタイプのプラットフォーム化を進める予定です。Hybridエミュレータでは複数のFPGAを搭載しているため、特定のFPGAにCPUコアを事前に搭載して検証プラットフォーム化し、空いたFPGAに周辺マクロなど製品ごとの回路を搭載することにより検証環境立ち上げ作業が効率化されます。これにより、検証品質の向上と検

図6 Hybridエミュレータによるプロセッサ設計検証環境

図7 マイコン評価プロセスの前倒し

証環境構築の効率化が期待できます。

### 8. おわりに

プロセッサ設計検証においてHybridエミュレータ導入により、設計・検証の期間短縮の効果を確認することができました。今後は、プロセッサ設計検証での利用にとどまらず、実チップと同等のプロセッサ性能評価・プロセッサ商品企画・プロセッサ仕様の事前確認およびプロセッサを含めた周辺環境/開発環境の整備として活用していく予定です。

#### 参考文献

- 1) Yuichi Nakamura, Kouhei Hosokawa, Ichiro Kuroda, Ko Yoshikawa, Takeshi Yoshimura, 19.2, 41st DAC 2004, "A Fast Hardware/Software Co-Verification Method for System-on-a-Chip by Using a C/C++ Simulator and FPGA Emulator with Shared Register Communication"

#### 執筆者プロフィール

山田 一男

NECエレクトロニクス

基盤技術開発本部

設計技術開発部

シニアデザインエンジニア

大東 正行

NECエレクトロニクス

マイクロコンピュータ事業本部

第一マイコン事業部

グループマネージャ

西本 浩秋

NECマイクロシステム

第二SoC開発事業部

主任

小野 洋彦

NECエレクトロニクス

マイクロコンピュータ事業本部

マイコンソフトウェア事業部

グループマネージャ