# SMP搭載カーナビゲーション用 システムLSI「ナビエンジン1」

吉田 正康・杉原 岳・高橋 敏明

河本 恭彦・石原 利憲

## 要旨

世界で初めてSMP型のマルチコアを使用したカーナビ向けシステムLSI“ナビエンジン1”の開発に成功しました。本稿では、開発に至ったカーナビの市場動向やベースとなったマルチコア技術、さらにはグラフィクスやLCDコントローラなど、ナビエンジン1が搭載している豊富な機能を紹介します。また、ナビエンジン1の開発で行った、車載機器向けデバイスとして要求される高い品質を大規模SoCの開発で実現する手法と、マルチコアで高い性能を達成するためのソフトウェアの事前評価や開発環境を構築するための活動について説明します。

## キーワード

- カーナビ ●マルチコア ●SMP ●グラフィクス ●LCDコントローラ

- シリアルATA ●車載対応 ●高品質 ●ソフトウェア開発環境

## 1. まえがき

### 1.1 カーナビ市場動向

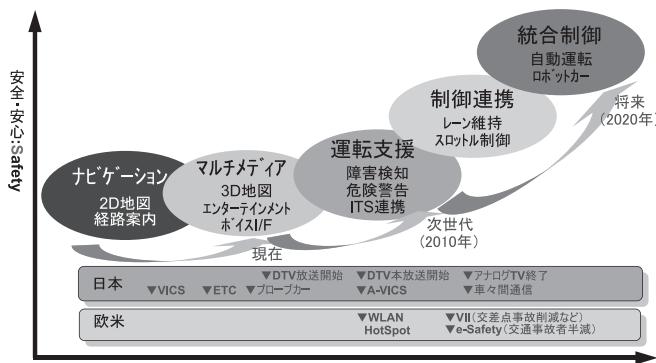

日本国内では、ふらりと乗ったタクシーや、道行く乗用車にカーナビが搭載されているのが普通になって久しいですが、海外でも空港の売店などで、GPS端末という名前でPND（ポータブル・ナビゲーション・デバイス）が当たり前で売られてきています。このように、カーナビ市場は全世界で年間1,000万台以上が売られ、さらに図1に示すように、今後車載カメラを活用してよりいっそうの安全・安心に寄与す

るようになっていくことが期待されています。

NECエレクトロニクスでも、今後の自動車のインテリジェント化に必須な頭脳部分を担う装置としてのカーナビの進化に期待し、注目分野としてマイコンを中心として半導体ソリューションの確立に努めてきました。

### 1.2 マルチコア技術

マイコンの技術動向として、マルチコア技術の発展・重要性が近年とみに高まってきており、高性能コンピュータのみならず、ゲーム機や携帯電話、デジタル家電でもマルチコアをベースにしたSoC（システム・オン・チップ）が広く活用されてきています。

特に、カーナビなど高性能を要求される分野では、従来の様々な機能に特化したマイコンやDSPなどを固定的に割り付ける機能分散システムを実現する非対称型マルチコア技術から、必要に応じて機能を動的に割り付ける負荷分散システムのための対称型マルチコア技術に注目が集まっています。

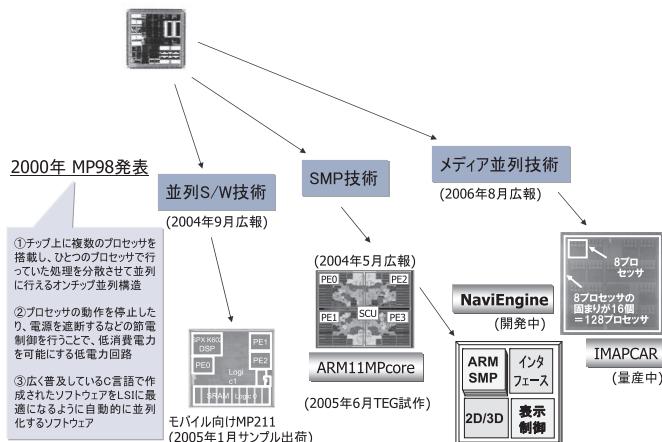

弊社では、これらマルチコア技術の開発に、図2にるようにNEC中央研究所とともに20年来、研究を続けてきました。この成果として2000年にはMP98技術を、また2005年には携帯分野向けSoCとしてMP211製品を発表してきました。

今回、カーナビ向けSoCとして世界で初めてSMP（対称型マルチコア・プロセッサ）技術を採用した“ナビエンジン1”的

図1 2020年に向けたカーナビシステムへの期待

## 自動車分野向け半導体 SMP搭載カーナビゲーション用システムLSI「ナビエンジン1」

図2 NECのマルチコア製品

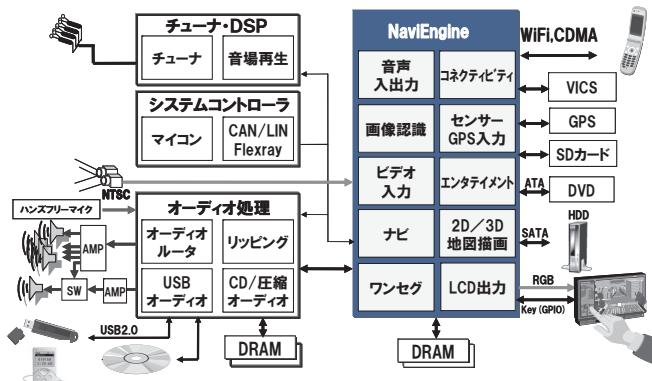

図3 ナビエンジンを用いたカーナビ・システム

製品開発に成功しました。ナビエンジン1を用いることにより、図3にあるような高機能・高性能なカーナビを構築することが可能となります。

ここに、"ナビエンジン1"製品自体の特徴とSoC化における開発のポイント、さらにマルチコアで着目すべきソフトウェア開発環境について紹介します。

### 2. ナビエンジン1の特長

#### 2.1 MPCore

ナビエンジン1は、CPUコアとしてARM製マルチプロセッサ

サMPCoreを採用しています。

MPCoreは、ARMv6命令セット、Thumb命令セットに加え、SIMD命令、Jazelle (Java高速化処理) に対応したRISC型マルチプロセッサです。

以下に主なMPCoreの特徴を示します。

- CPUコア：ARM11マイクロプロセッサ・アーキテクチャCPUを4個搭載

- 大容量1次キャッシュメモリを内蔵

- 命令キャッシュ：1 CPUあたり32Kバイト

- データキャッシュ：1 CPUあたり32Kバイト

- 分岐予測およびホールド機能を備えた8段パイプライン

- VFPコプロセッサを各CPUコアに装備

- 最大動作周波数：400MHzで動作

- 処理性能：1920DMIPSを実現

- システムバス：デュアル64ビットAMBA3 AXIシステムバスを採用

- キャッシュ・コヒーレンシー：最適化されたMESIコヒーレンシプロトコルを使用し、処理効率を向上

ナビエンジン1は、この高性能なMPCoreを採用することにより、マルチメディア処理や、画像認識による走行支援など高い処理能力を必要とする高機能高性能カーナビ・システムに最適な構成となっています。

#### 2.2 2D/3Dグラフィックス・エンジン

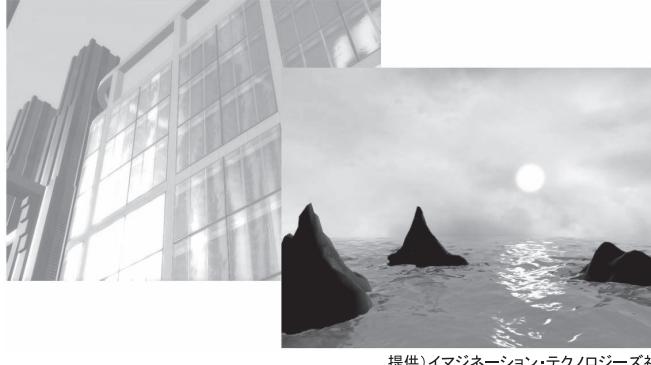

ナビエンジン1では、カーナビ機器に必須となる2D/3Dグラフィックス・エンジンとして新世代アーキテクチャに対応したイマジネーション・テクノロジーズ社製PowerVR SGXファミリのSGX535を採用しています。

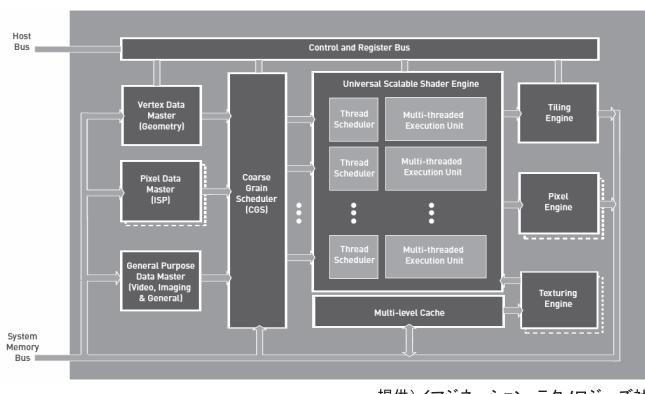

SGX535は新世代アーキテクチャであるプログラマブルシェーダを採用し、図4にあるような高品位な3D画面の描画を行うとともに、マルチスレッド構成により2次元Dと3次元の同時描画を実現した高性能GPU (グラフィックス・プロセッサ・ユニット) です。図5にSGX535のブロック図を示します。

以下にSGX535の主な特徴を示します。

- プログラマブルな頂点処理とピクセル処理を可能とするユニバーサル・スケーラブル・シェーダー・エンジン (USSE) 2基搭載

- タイリング方式により、メモリバンド負荷を軽減

- OpenGL 2.0、OpenGL ES 2.0、DirectX 9のすべての3D機能

図4 PowerVR SGX描画イメージ図

図5 PowerVR SGXブロック図

を搭載

- ・マルチスレッド対応により、2D/3D描画を平行して実行可能

- ・業界最高水準の描画コア性能

- ・頂点処理性能：15Mポリゴン/秒

- ・ピクセル描画性能：約800M画素/秒（隠面消去効果考慮）

### 2.3 ディスプレイ・コントローラ

ナビエンジン1は、マルチメディア処理に対応したAVN（オーディオ・ビジュアル・ナビゲーション）カーナビ・システムに最適なディスプレイ・コントローラを内蔵しています。

以下に主な特徴を示します。

- ・マルチウィンドウおよび高精細な地図描画を可能とする7レイヤ画面合成

- ・高精細ディスプレイ WSVGA (1024×600ピクセル) に対応。レイヤ数を制限することで最大WXGA (1280×768ピクセル) にも対応可能

- ・豊富な透過機能（レイヤ透過、ピクセル透過、カラーキー（クロマキー））

- ・各レイヤ独立な拡大/縮小機能

- ・画像補正機能（ディザ、ブライテネス、ガンマ補正）

- ・ハードウェア・カーソルを内蔵

- ・ラウンドラップ機能に対応

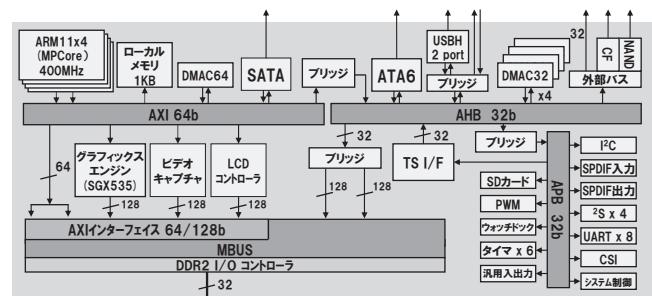

### 2.4 その他のIP

このほかに、ナビエンジン1はMPCoreの高い処理能力を生かすため、ミドルウェアによるワンセグ再生や、画像認識を可能とするTS（トランスポート・ストリーム）インターフェース、ビデオキャプチャ機能を搭載しています。また、PC向けハードディスク・ドライブ市場がATAからシリアルATAへ切り替わりつつあることから、ATA、シリアルATAの両インターフェースを搭載しています。また、携帯端末とのコネクティビティを考慮し、USBホストを2ポート装備など、AVNの特徴があります。

### 3. SoC開発にあたっての留意点

#### 3.1 内部アーキテクチャの特徴

図6にナビエンジン1の内部ブロック図を示します。弊社では、カーナビSoC開発のプラットフォーム化を推進しており、

図6 NaviEngine1 ブロック図

## 自動車分野向け半導体

### SMP搭載カーナビゲーション用システムLSI「ナビエンジン1」

ナビエンジン1もそれにのっとることで開発の短TATを実現しました。特にバス性能を必要とするディスプレイ、ビデオキャプチャ、2D/3Dグラフィックスなどについては、MPCoreの出力ポートにならって、マルチレイヤ・バスであるAXIバスを採用してスループットを向上させています。また、処理性を重視したMPCoreには4CPU構成を採用しています。

#### 3.2 車載を意識した取り組み

車載製品はその性格上、10ppm以下の不良率を求められます。そこで故障検出率の目標を單一縮退故障で99%以上、遷移故障は97.5%以上に定めました。この数値を実現するため、ナビエンジン1ではDFT（デザイン・フォー・テスティング）の手法を全面的に取り入れ、Logic Vision社のロジックBISTとメモリBISTを採用しています。また、各搭載ハード・マクロの単体テスト・モードの実装はもちろんのこと、ロジックBISTでは原理的に故障を検出できないクロック分周回路に関しては外部からクロックをモニタする機能を設けました。これらの施策により、目標の検出率を達成しています。

#### 3.3 開発の効率化

ロジックBISTとメモリBISTを短期間で実装するために、その分野では先駆者であるNECエレクトロニクス・ヨーロッパのテクノロジ・センタと連携して開発を行いました。特に、日本とヨーロッパの時差を有効に使うことで、データの生成と検証を効率的に行うことができました。

また、ナビエンジン1には完全に新規設計を行ったマクロが5個以上含まれており、設計不具合の混入の恐れがありました。これに対して開発チームは「ES一発完動」を合言葉に、FPGAを用いたプロトタイピング試作を行い、可能な限り実際の動作環境で評価を行いました。その結果、ナビエンジン1のESでは大きなバグもなく「ES一発完動」を達成することができました。

## 4. ソフトウェア開発環境

### 4.1 マルチコア向けソフトウェア開発の課題

ナビエンジン1では、カーナビとしては革新的なSMP型のマ

ルチコア技術を採用しました。このため、ソフトウェア開発の大きな課題として、(1)対象システムに対するマルチコア・ソリューションの有効性を確認すること、(2)膨大な既存ソフト（シングルコア向け、組込み特有のチューニングを含む）を、マルチコアOS上で動作させること、(3)ハードウェア性能を最大限に引き出す、流用性や拡張性に優れたソフトウェア構造にリファクタリングすること、がありました。これらの課題を解決することにより、ナビエンジン1の性能を最大限引き出す、高性能システムの短期開発が可能になります。しかし、膨大な既存ソフトウェアの存在、また、マルチコア向けソフトウェアの複雑さを考慮すると、上記課題の短期解決は非常に困難です。

したがって、現実的には、(1)、(2)、(3)の順番で、可能な部分から順次マルチコア対応を進めました。

#### 4.2 ナビエンジン1で行った工夫

前述の課題(1)の解決のため、ナビエンジン1、そしてSMP OSが存在しない時期である2005～2006年にかけて、独自のアプリケーション並列動作解析ツールを作成し、既存のカーナビ・ソフトウェアをナビエンジン1上で実行してもシステム性能向上が図れること、また、SMP動作機構としてのオーバヘッド（性能劣化）が十分に小さいこと、つまり、ナビエンジン1のカーナビ・ソフトウェアに対する有効性を確認しました。また、その他解析結果も含めて、SoC設計にフィードバックし、より有効性を高めました。

#### 4.3 OS対応など

ソフトウェアのマルチコア対応化では、デバッガ、システム解析ツール、チューニング・ツールなどの、組込みソフトウェア開発ツールが重要になります。ナビエンジン1に接続可能なマルチコア対応ICE（インサーキット・エミュレータ）はすでに複数種類が利用可能になっています。OSを含むその他ソフトウェア開発ツールは、ツールベンダやフォーラムで開発中で、順次使用可能になる予定です。これらのツール群の拡充により、課題(2)および(3)を解決する環境が整えられることになります。弊社はこれらのサードパーティ連携活動に積極的に貢献しています。

## 5. 今後の展開

弊社は、ナビエンジン1を1つの製品にとどまらず、下記の技術を中心とした基本アーキテクチャと捉えています。

- ・マルチコアによるスケーラビリティ

- ・必要な帯域を確保する高性能内部バス

- ・高品位ユーザインターフェースを実現するグラフィックス・エンジン

今後、このアーキテクチャをベースとした複数のSoCを開発し、製品展開を図っていく所存です。

これにより、ナビエンジンをご使用いただいたお客様に、少ないソフトウェア開発コストで、複数の世代にわたりいくつもの仕向け先に応じた多数のカーナビ製品展開の実現に寄与することができます。

また、基本アーキテクチャは継続的に改善し、よりいっそろの高性能化、低消費電力化、コスト効率化を進め、ミドルウェアなどによるカーナビ製品の高付加価値化に向けての提案を進めています。

## 6. むすび

今回開発しましたナビエンジン1は、今後ますます重要度が増していくカーナビの中核となるSoCです。ナビエンジンのアーキテクチャを進化させることにより、自動車システムの頭脳を実現したいと考えています。

また、我々は今回の開発を通じて、高性能・高機能のための最先端プロセスによる高集積SoCを、車載に耐えうる高品質で開発するための開発フローを確立しました。このノウハウは、車載製品に限らず、今後の大規模SoC開発に適用できる貴重な資産になるとを考えています。

さらに、ナビエンジンをベースにマルチコアでのソフトウェア開発のプラットフォームの構築を進めています。このプラットフォームは弊社のマルチコア技術を中心としたソード・パーティ各社を交えたマルチコア対応ソフトウェアを揃え、お客様に幅広い機能の選択肢を提供します。

これらの活動を通じ、弊社のマイコン・SoC開発におけるコンピタンスの向上を図っていきます。

\*ARM、AMBA、JazzelleはARM社の登録商標です。

\*ARM11、MPCore、AXIはARM社の商標です。

\*PowerVRはImagination Technologies社の商標です。

\*LogicVisionはLogicVision社の商標です。

## 執筆者プロフィール

吉田 正康

NECエレクトロニクス

マイクロコンピュータ事業本部

自動車システム事業部

杉原 岳

NECエレクトロニクス

マイクロコンピュータ事業本部

自動車システム事業部

高橋 敏明

NECエレクトロニクス

マイクロコンピュータ事業本部

マイコンソフトウェア事業部

河本 恭彦

NECマイクロシステム

第二SOC開発事業部

プロセッシングプラットフォームグループ

石原 利憲

NECマイクロシステム

第二SOC開発事業部

プロセッシングプラットフォームグループ