# 高速通信を可能にする携帯電話用ベースバンドLSI(M2)の開発

田中秀夫・中山貴司・徳江達也

**要旨**

W-CDMAのHSDPA、およびGSM/GPRSに対応した高性能ベースバンド機能と、アプリケーション機能を同一チップに搭載した携帯用ベースバンドLSI「M2」を開発しました。「M2」は、先端プロセスである65ナノプロセス技術を行い、回路設計、およびレイアウト設計の両面から様々な低消費電力化技術を採用、チップの小型化を図るとともに、高速化・低電力化を実現しました。

**キーワード**

●W-CDMA ●ベースバンド ●携帯電話 ●アプリケーション ●低消費電力

## 1. はじめに

2001年のサービス開始以来、UMTS(Universal Mobile Telecommunications System、日本国内では、W-CDMA：Wideband Code Division Multiple Accessと呼称)は第3世代携帯電話として着実な普及・拡大を果たすとともに、市場でもより高機能、高性能な要求が増えています。このため、種々の高度なアプリケーション処理が必要となり、取り扱うデータ量も膨大で、高速・大容量通信が求められています。本稿では、この高性能・高機能を実現し、かつ携帯電話に適した低消費電力化を追求したLSI(M2)の開発について述べます。

## 2. M2開発の背景

W-CDMAにおいて、高速、大容量の通信を実現する方法としてHSDPA(High Speed Downlink Packet Access)、HSUPA(High Speed Uplink Packet Access)があり、この機能の内蔵、もしくは対応が必要になっています。

また、携帯端末普及の鍵は、World-Wideへの展開であり、これには、すでに世界的にインフラが整備されているGSM/GPRS(Global System Mobile communication/ General Packet Radio Service)への対応、すなわち、W-CDMAとGSM/GPRSのローミングを可能にするDual機能の対応が必要となっています。さらに、アプリケーション面に目を向けると、高速・高精細の画像処理、地上デジタル放送対応など高度な機能を搭載する必要があります。このような高性能・高機能化を実現する

には、LSIとしては高速処理、および大規模回路の集積が必要になります、携帯電話で要求される低消費電力という命題に相反するものとなります。そこでいかに低消費電力化を実現するかが大きな課題となります。

また、性能・機能面の向上だけでなく、携帯端末として装置搭載面積削減のため、パッケージの小型化も求められることになります。以上のことから、これら複合的な機能を内蔵し、かつ、携帯電話に適した低消費電力化・小型化のベースバンドLSI(M2)の開発が進められました。

## 3. M2の開発目標

M2は、高度なベースバンド機能と高性能なアプリケーション機能を搭載したLSIであり、下記機能・性能を目標に開発を行いました。

- HSDPA機能、HSUPA インタフェース機能の内蔵

- GSM/GPRS機能を内蔵し、Dual動作の実現

- 画像処理機能の向上のため、CPU、DSPの高性能化

- 音源機能の内蔵

- 前製品であるM1と同等の低消費電力の実現

- 市販メモリを積層できるPoP(Package on Package)構造

## 4. M2のアーキテクチャ

M2は、前製品であるM1（表）のアプリケーションに対し、機能追加、性能強化するとともに、ベースバンド部として

GSM/GPRS機能、HSDPA機能を内蔵したアーキテクチャとなります。図1にM2のブロック図を示します。

アーキテクチャの特徴は以下になります。

- モジュール間の性能確保のため、AHB、AXIバスを採用、ベースバンド部とアプリケーション部はAXIバスで結合。

- ベースバンド部は、制御を行うARM11を含んだCTOP部

表 M2概略仕様とM1

|       | M2                                                                                                    | M1                                                                     |

|-------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 製品名   | $\mu$ PD77620                                                                                         | MC-10038F1                                                             |

| 搭載機能  | アプリケーション/W-CDMA機能<br>HSDPA(3.6Mbps)機能内蔵<br>(外付けLSIで7.2Mbps可能)<br>HSUPAコプロセッサIF内蔵<br>音源機能、GSM/GPRS機能内蔵 | アプリケーション/W-CDMA機能<br>GSM/GPRS IF機能内蔵                                   |

| 回路規模  | Logic: 15M gate, ROM: 1.6Mbit<br>SRAM: 12Mbit (1p), 0.5Mbit (2p)                                      | Logic: 7M gate<br>SRAM: 8Mbit (1port), ROM: 0.5Mbit                    |

| 動作周波数 | アプリ部: ARM1176, DSP(500MHz動作)<br>DBB部: ARM1156, DSP(250MHz動作)<br>DDR I/F: 166MHz                       | アプリ部: ARM926, DSP(250MHz動作)<br>DBB部: ARM926(123MHz)<br>DDR I/F: 125MHz |

| プロセス  | 65nmプロセス<br>Tr: LowVt/MiddleVt/HighVt混在                                                               | 90nmプロセス<br>Tr: LowVt/MiddleVt/HighVt混在                                |

| 電源電圧  | 内部 1.2V±0.1V、<br>I/O部 3.0V±0.3V, 1.8V±0.1V                                                            | 内部 1.2V±0.1V、<br>I/O部 3.0V±0.3V, 1.8V±0.1V                             |

| パッケージ | FCBGA(PoP) 14mm□, 529pin                                                                              | 0.5 mmピッチFPBGA, 14 mm□, 529pin                                         |

| その他   | 新技術採用(LongRun2、電源SW)<br>メモリリダンダンシー適用<br>リダンピア適用                                                       | メモリリダンダンシー適用                                                           |

図1 M2ブロック図

と信号処理を行うWTOP部で構成。

- GSM/GPRS部、およびHSDPA部はベースバンド部に内蔵し、ベースバンド側で制御。

- アプリケーション部は、待機時に動作必要なL0領域と通常動作のL1領域に分割。

## 5. 低消費電力化実現への課題

前製品のM1は、搭載装置(SIMPULE N1)がW-CDMA携帯電話では世界最高クラスの稼働時間（連続待受時間700時間（静止時）、連続通話時間が210分）を誇っており、M1はその実現に大きく貢献しました。M2では、その低電力を維持することが求められました。

一般に消費電力は、動作電力（回路の動作による電力消費）とリーク電力（漏れ電流による電力消費）に分類されます。携帯電話用LSIの場合、動作電力を小さくすれば通話時間が伸び、リーク電力を小さくすれば待受け時間が伸びます。

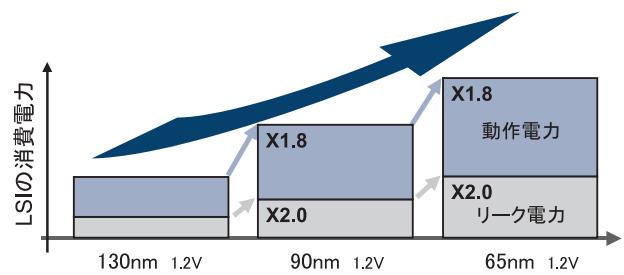

ここで、半導体プロセスの微細化による電力のトレンドを説明します。回路規模と速度が同一なら、半導体プロセスの世代とともに動作電力は減りますが、リーク電力は変わりません。しかしながら、プロセスを1世代進めると同一チップサイズに入るゲート規模は2倍、速度は1.3倍になります。このメリットを享受するのが普通です。その場合、動作電力、リーク電力ともに2倍程度増えてしまいます（図2）。

- 動作電力: 1.8倍 = ゲート規模 2倍 × 速度 1.3倍 × 1ゲートごとの動作電力 0.7倍

- リーク電力: 2.0倍 = ゲート規模 2倍 × 1ゲートごとのリーク電力 1倍

M2と前品種のM1は、まさにこのような関係になります。表にあるようにM2で機能追加と性能向上を行ったため、回路規

図2 電力比較(プロセス世代とともに回路規模と速度を増大)

## デジタルコンシューマ分野向け半導体 高速通信を可能にする携帯電話用ベースバンドLSI(M2)の開発

模は約2倍となり、これを同等のパッケージサイズ（チップサイズ）に収めるためにプロセスを一世代進めました。求められる性能も上がっており、速度（動作周波数）も1.3～2倍になっています。このままでは、動作電力、リーク電力共に2倍近くなり、通話時間が減ってしまいます。そのため、リーク電力と動作電力を半減させてM1と同等にすることが、M2の設計目標となりました。

### 6. 採用した低消費電力化技術

#### 6.1 動作電力削減

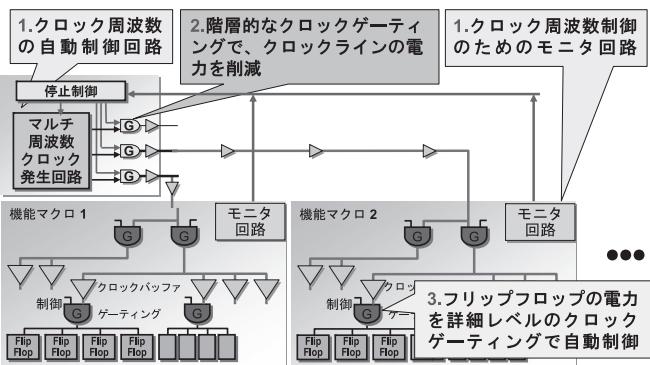

通話時間を延ばすための動作電力削減技術として、自動クロック制御技術を採用しました。動作電力は信号の動作率（周波数）に比例するため、必要最低限の動作で済むようクロックを停止させる方法(clock gating)や、必要に応じて周波数を下げる方法(dynamic frequency control)が一般に使用されています。これらのクロック停止や周波数制御はソフトウェアの指定で行なうことが一般的ですが、人手による最適化が必要であるため、すべての場合において最小の電力に保つようなソフトウェアを作成することは困難です。この問題を、ハードウェアによる自動制御を取り入れることで解決しました。**図3**は、アプリケーションCPUや各種処理回路などの機能マクロのクロック系統回路を示したものです。

- 1) 機能マクロごとに動作状況を監視するモニタ回路を設け、低負荷状態と判断すると自動的にシステムクロック周波数を低下させて、電力を低減します。

- 2) 上記モニタ回路で機能マクロが動作停止状態と判断する

図3 自動クロック制御

と、クロックラインの電力をカットします。また、アプリケーションCPUが一定時間停止している場合は、CPUの電源スイッチ（後述）をオフすることで、リーク電力も削減しています。

- 3) 機能マクロ内のクロックは綿密かつ階層的にゲーティングしており、無駄なクロック動作を抑制します。

#### 6.2 リーク電力削減

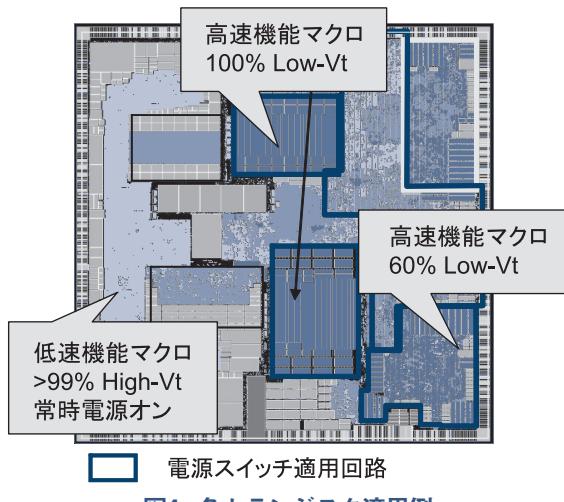

待受時間（着信待ち状態の待機時間）は主にリーク電力（何も動作しないときに流れる漏れ電流による電力）によって決まります。M2では待受時間を延ばす低消費電力技術として、3種類のトランジスタと待機時のリーク電力をカットする電源スイッチを搭載しました。

Vt（閾値）の異なる下記3種類のトランジスタを用途によって使い分けることで、高速動作と低リーク電力の両立を実現しています。

##### 1) HighVt

低速だがリーク電力は少ない。常時電源オン状態のデジタルベースバンド部の回路で主に使用しました。

##### 2) MiddleVt

HighVtより1.5倍高速だが、1桁リーク電力が多い。HighVtでは速度が不足する回路に一部使用しています。

##### 3) LowVt

HighVtより2倍以上高速だが2桁リーク電力が多い。500MHz動作が必要なアプリケーション用CPU、DSPに適用しました。

LowVtトランジスタを適用した回路はリーク電力が数mW～数10mWとなるため、待受け時には電源を切っておく必要があります。M2ではLowVtを適用した7系統の回路に電源スイッチを内蔵し、各回路が未使用時に個別に電源を切ることでリーク電力を削減しました。LSI外部での電源オン・オフに比べ電源スイッチにより、よりきめ細かな電力制御が可能となりました。M2のアプリケーションCPUでは、OSの待機状態で電源オフし、割り込み信号により数μsecで起動ができるため、ソフトウェアによる使いやすい省電力機能が実現できました（**図4**）。

図4 各トランジスタ適用例

図5 自動クロック制御と電源スイッチの効果

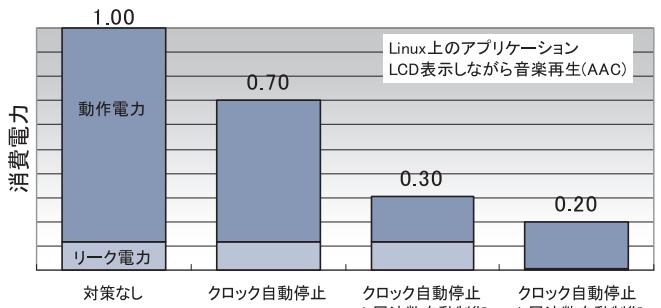

### 6.3 消費電力削減効果

上記のような低消費電力化技術を駆使することにより、M2の電力消費はM1と同等に抑えることに成功しました。

実アプリケーションを動作させての評価結果を図5に示します。評価に用いた音楽再生アプリケーションは処理自体は軽いため、動作周波数500MHzのCPUで実行させるには、最も電力削減効果が望まれるものです。クロック自動制御と電源スイッチ制御により、消費電力を1/5することができました。

### 7. M2の成果

M2はアプリケーションとベースバンドを統合した大規模回路にもかかわらず、チップサイズ8.52×8.52mm<sup>2</sup>に集積する

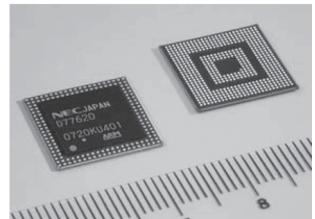

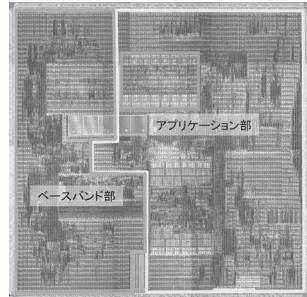

写真 M2チップと製品外観

ことができました。また、パッケージは、当初予定していました汎用メモリチップが搭載可能な529pinのPoPで実現できました。写真にチップ写真と製品外観を示します。

さらに、M2は65nmの最先端プロセスを使用していることもあり、量産性の観点からメモリリダンダントークン、リダンビアを適用しましたが、適用率はそれぞれ60%（約7Mbits）、55%となり、十分、量産性を確保することができました。

このM2を用い、前製品であるM1と同等の世界最高水準の待ち受け時間、通話時間を実現することができます。

### 8.まとめ

M2は、65nmの最先端のプロセスを用い、従来製品のM1に比し、搭載規模が倍以上になったにもかかわらず、低消費電力化技術を駆使することにより、M1に匹敵する電力性能を達成、携帯端末の性能向上に寄与できました。今後もアプリケーション、通信性能の高機能・高性能化の進展が予想されますが、携帯端末に適した低消費電力化を追求していくとともに、新しい技術を取り込み、お客様に満足いただけるLSIを開発、提供していく所存です。

### 執筆者プロフィール

田中 秀夫

NECエレクトロニクス

第二SoC事業本部

モバイルLSI事業部

中山 貴司

NECエレクトロニクス

第二SoC事業本部

モバイルLSI事業部

徳江 達也

NECエレクトロニクス

第二SoC事業本部

モバイルLSI事業部