# HD DVDプレーヤ/レコーダ用LSI EMMA3

松永 光浩・坪井 栄二・下嶋 覚

中溝 正樹・五嶋 宏之

## 要 旨

NECエレクトロニクスは、世界で初めてHD DVDプレーヤとレコーダに対応したシステムLSIを発売しました。このLSIは、HD DVDプレーヤに必要なデジタル映像、音声、グラフィックス処理を行います。次世代DVDで採用されている「MPEG-4 AVC/H.264」や「VC-1」などの映像、音声の圧縮規格に対応し、高度なアプリケーションに対応できます。また、デジタル放送記録のためのストリーム処理やマルチチャネルストリーム入出力を備えているため、HD DVDレコーダへシステムの拡張が可能となっています。

## キーワード

- HD DVD

- プレーヤ

- レコーダ

- システムLSI

- デジタル放送

- デジタル・ハイビジョン放送

- MPEG-4 AVC/H.264

- VC-1

## 1. まえがき

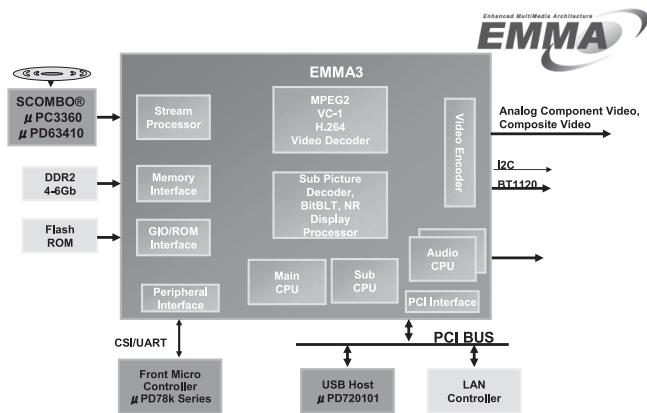

近年、BSデジタル放送、地上デジタル放送のデジタル・ハイビジョン放送の受信可能地域が広がり、テレビ受信機のデジタル・ハイビジョン対応が急速に進んでいます。また、ディスク・メディアでもよりきれいに映像を見たいというユーザ要求に応えて、次世代DVDのHD DVDではデジタル放送と同じデジタル・ハイビジョン画質に対応しました。高画質化とともにディスク・メディアのインターラクティブ性を活用したコンテンツが急速に広まっています。これらのコンテンツを再生するプレーヤは急速に普及価格帯へのシフトが始まっているため、高機能化と同時にシステム・コストを低減できるようなシステムLSIの開発を強く求められています。NECエレクトロニクスは、このような市場の動向を踏まえて、HD DVDプレーヤの機能とデジタル・ハイビジョン放送に対応したHD DVDプレーヤ、レコーダLSI「EMMA<sup>TM</sup> 3」を世界で初めて発売しました（写真1、図1）。

## 2. EMMA3の特長

EMMA3は、次の特長があります。

### 1) HD/SDの同時デコード

HD DVDプレーヤに必要なMPEG-4 AVC/H.264、VC-1、MPEG2 MP@HLの(HD+SD) 同時デコードが可能です。

写真1 EMMA3 (μPD61335)

図1 EMMA3ブロック図

また、デジタル・ハイビジョン・レコーダに求められる2番組のデジタル・ハイビジョン放送の同時受信、録画を1chipで実行することも可能です。

### 2) 高性能ストリームプロセッサ搭載

HD DVDとデジタル放送に対応した柔軟かつ高速なストリーム処理機能を提供します。これにより、インターネットを使ったHD DVDのインタラクティブ・ストーリー、ハイブリット再生も可能です。

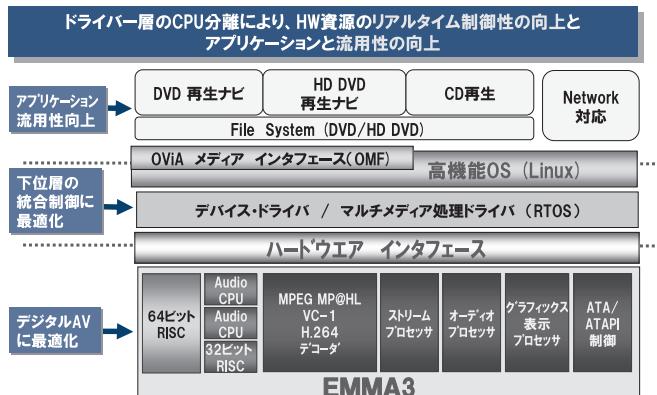

### 3) 2CPUアーキテクチャ採用

EMMA3はメインCPUとサブCPUをアプリケーションとドライバが使用します。ハードウェアに近いドライバのリアルタイム処理をサブCPUが担当し、メインCPUをインタラクティブなユーザ・アプリケーションに開放します。2CPUの機能分担により、ユーザのシステム開発を容易にします。

## 3. EMMA3の機能概要

### 3.1 CPU

メインCPUは、弊社オリジナルの64bit RiSC CPUのVR5500です。64Kbyteの命令キャッシュと、データキャッシュを内蔵し、アプリケーションに柔軟に対応するハイ・パフォーマンスCPUです。

サブCPUは、MIPSテクノロジー社の32bitのRiSC CPUです。8Kbyteの命令キャッシュと、データキャッシュを内蔵し、リアルタイム性が要求されるドライバ、AV処理を分担します。

### 3.2 ストリームプロセッサ

弊社独自のストリーム処理に特化した専用プロセッサです。DVD-Video、DVD-Video Recording、ARIBのデジタル放送など多種多様なストリームに加え、HD DVD規格にも柔軟に対応が可能です。

### 3.3 ビデオ・デコード・エンジン

MPEG2 MP@HL、MPEG1に加えてMPEG-4 AVC/H.264、VC-1に準拠したビデオ・デコーダ・エンジンを搭載しています。MPEG2 MP@HLのデュアル・デコードに対応することにより、デジタル放送の視聴とともに同時に別番組をデコード、

再エンコードしてDVD-Video recordingフォーマットに変換するためのSDダウンコンバート・デコードも可能です。

### 3.4 オーディオ・デコード・エンジン

オーディオ・デコード・エンジンに32bitのRiSC CPUを2個搭載しています。Dolby Digital Plus、True HD、DTS-HDなどの音声フォーマットやエフェクト・オーディオの同時再生に対応しています。

### 3.5 ユニファイド・メモリ・アーキテクチャ

メモリを使用するすべてのユニットからのデータ転送要求を処理します。2系統のDDR2 SDRAMインターフェースに連続したアドレス空間を割り当てるユニファイド・メモリ・アーキテクチャをサポートします。DDR2 SDRAMインターフェースは655.36MHzの32bitバスと16bitバスの2系統に独立してアクセスが可能であり、最大で8192Mビットのメモリを接続することが可能です。

### 3.6 DMAコントローラ

TS入力/デマルチプレクサ、MPEGデコード・エンジン、オーディオ・デコード・エンジンの内部ユニットとDDR2 SDRAMとの間のDMA転送、およびDDR2 SDRAMからDDR2 SDRAMの間の高速なDMA転送が可能です。また複数のDMAをCPUの介在なしに自動実行することが可能です。これにより細分化したデータのコピー、転送のCPU負荷を軽減します。

### 3.7 拡張メモリ・インターフェース

NOR型フラッシュ、NAND型フラッシュの接続をサポートし、外部ROMインターフェースとして最大4つのチップ・セレクト信号、64Mバイトの領域をサポートします。汎用I/Oインターフェースとしては、最大4つのチップ・セレクト信号と、各チップ・セレクトに16Mバイトの領域をサポートしています。

### 3.8 ATA/ATAPIインターフェース

業界標準であるパラレルATAインターフェース2チャンネル内

## デジタルコンシューマ分野向け半導体 HD DVDプレーヤ/レコーダ用LSI EMMA3

蔵しており、PIOモード、Ultra-DMA100をサポートしています。それぞれのマスタ、スレーブにハードディスク、光学ドライブを接続することで最大4ドライブまで対応可能です。

### 3.9 ディスプレイ・コントローラ/BitBLTエンジン

次世代DVDに対応するために強力なディスプレイ・コントローラ・エンジンを内蔵しています。

メイン・ディスプレイは、HDサイズの2つのビデオ・プレーン、4つのOSDプレーン、1つのバックカラーをサポートしています。アンチリッッカー・フィルター、256レベルのアルファ・ブレンディング、SD用動き適応形IP変換、各種ノイズリダクションに対応しています。

サブディスプレイは、従来のアナログTVに対応しています。SDサイズの1つのビデオ・プレーン、1つのOSDプレーンをサポートしています。さらに、レコーダの他チャンネル・ダウンコンバート録画に対応するデジタル出力があります。

OSDのフォーマットは、2、4、8ビット/ピクセルのカラー・ルックアップ・テーブルとRGB32、RGB16をサポートします。αブレンディングによる透過処理などにも対応しています。

BitBLTエンジンは、2次元イメージの高速なブロック転送機能や、フォント展開などに有効なカラー・スペース・コンバージョン、サイズ変換などの機能をサポートしています。

### 3.10 外部ビデオ／オーディオ入出力

外部入力として、ITU-R BT.656フォーマットのデジタル・ビデオ・インターフェースとPCMのオーディオ入力をサポートしています。

外部出力として、HDMIなどのデジタル出力のためITU-R BT.1120/BT.656に準拠したデジタル・ビデオ出力をサポートしています。また、オーディオ出力は、PCMデータ、および、S/PDIFからストリーム・データを出力することが可能です。

### 3.11 ビデオ・エンコーダ

デジタル・ビデオ出力のメイン・ビデオ、再エンコード用出力に加えてアナログ・ビデオ出力のメイン・ビデオとサ

ブ・ビデオが可能です。アナログのメイン・ビデオ出力では、148MHz 10-bit DACよりYPbPr/YCbCr出力が可能です。サブ・ビデオ出力では、54MHz 10bit DACよりコンポジットビデオ出力、もしくは、Y/Cビデオ出力が可能です。

### 3.12 各種周辺機能

その他周辺機能として、33MHz 32bit PCI 2.2準拠のPCIバス・インターフェースとUARTを3系統、I2Cを3系統、CSIを3系統、スマートカード・インターフェースを1系統、IRトランスマッタを1系統などHD DVDのプレーヤ、レコーダに必要なほとんどの周辺機器インターフェースを内蔵しています。EMMA3の仕様一覧を表に示します。

### 4. ソフトウェア・アーキテクチャ

EMMA3の標準ソフトウェア構成例を図2に示します。リアルタイム性が要求されるハードウェア制御などはサブCPUのRTOS上で実行します。ユーザ・アプリケーションはメインCPUのLinuxで実行します。CPU間の情報はCPU間通信ドライバが行います。CPUの役割が明確なこの構成を採用すること

表 EMMA3の仕様一覧

|                      |                                                                                                                                                                                                                                                                                                              |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Video decoder        | <ul style="list-style-type: none"><li>MPEG2 video MP@HL, MP@ML standard, MPEG1 video standard</li><li>MPEG4 AVC/H.264 HP@L4.1, MP@L4.1, L3.2</li><li>VC1 AP@L3, AP@L2, full trick play, JPEG decode accelerator</li><li>MPEG4 ASP@L5 visual standard without 1/4 pixel, global motion compensation</li></ul> |

| Audio decoder        | <ul style="list-style-type: none"><li>Dolby™ Digital, Dolby Digital Plus, Dolby True HD, DTS™, DTS-HD</li><li>MPEG1 Layer 1/2, MPEG2 AAC, MLP, LPCM for DVD, CD-DA, MP3, WMA</li></ul>                                                                                                                       |

| Stream processor     | <ul style="list-style-type: none"><li>Based on HD DVD, DVD-Video, DVD-Video Recording, DVD+VR, Video CD 2.0, ARIB, MPEG2-TS, MPEG2-PS and MPEG1</li></ul>                                                                                                                                                    |

| Scramble functions   | <ul style="list-style-type: none"><li>CSS descrambler, CPRM, AACS scrambler / descrambler</li><li>DES, 3-DES, AES encryption / decryption engine</li><li>Multi-2 ARIB</li></ul>                                                                                                                              |

| Main CPU             | <ul style="list-style-type: none"><li>64/32-bit RISC, 655 Dhrystone MIPS at 327 MHz frequency</li></ul>                                                                                                                                                                                                      |

| Sub CPU              | <ul style="list-style-type: none"><li>32-bit MIPS32™ CPU Core, 457 Dhrystone MIPS at 327 MHz frequency</li></ul>                                                                                                                                                                                             |

| Storage interface    | <ul style="list-style-type: none"><li>Two parallel ATA / ATAPI interfaces, Ultra-ATA100</li></ul>                                                                                                                                                                                                            |

| Video encoder        | <ul style="list-style-type: none"><li>NTSC / PAL / SECAM / HDTV (720p / 1080i / 480p / 576p)</li><li>simultaneous YPbPr, Y/C analog output</li></ul>                                                                                                                                                         |

| Digital video output | <ul style="list-style-type: none"><li>ITU-R BT.656, 1120</li></ul>                                                                                                                                                                                                                                           |

| Digital audio output | <ul style="list-style-type: none"><li>IEC61937</li></ul>                                                                                                                                                                                                                                                     |

| Peripherals          | <ul style="list-style-type: none"><li>I2C, clocked serial interface, UART, timer</li></ul>                                                                                                                                                                                                                   |

| PCI                  | <ul style="list-style-type: none"><li>3.3V 32-bit PCI at 33MHz</li></ul>                                                                                                                                                                                                                                     |

| Unified memory       | <ul style="list-style-type: none"><li>32/48-bit bus width, DDR2-667 SDRAM</li></ul>                                                                                                                                                                                                                          |

| ROM interface        | <ul style="list-style-type: none"><li>NOR / NAND Flash ROM</li></ul>                                                                                                                                                                                                                                         |

| Power supply         | <ul style="list-style-type: none"><li>1.0V, 1.8V and 3.3V</li></ul>                                                                                                                                                                                                                                          |

図2 EMMA3ソフトウェア構成

により、ユーザはアプリケーション開発に専念することができ、セットの差別化に貢献します。

弊社が提供するソフトウェアは、CPU間通信以下のドライバ・ソフトウェアであり、ハードウェアを直接意識しない共通的なインターフェースを持っています。

このソフトウェア・インターフェースは、今後のEMMAファミリで共通的に使用することが可能なため、ソフトウェア資産を流用することが可能となっています。また、メインCPUのOSに業界標準であるLinuxを採用することにより、ユーザのソフトウェア開発効率の向上に開発期間の短縮で貢献します。

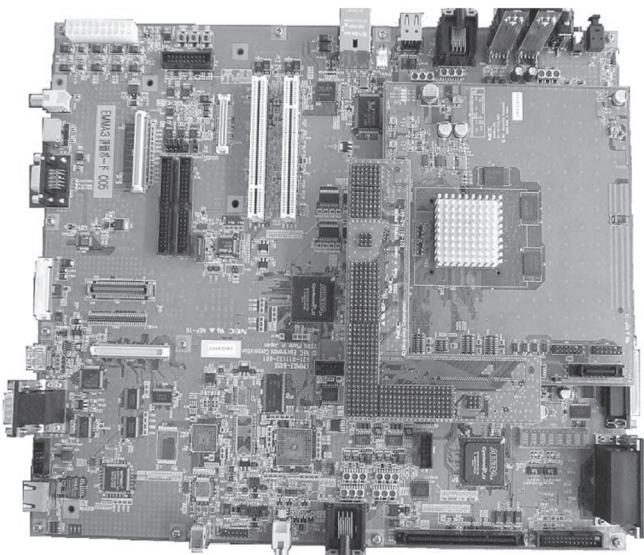

写真2 EMMA3評価ボード

## 5. 開発環境

EMMA3の評価ボードを写真2に示します。この評価ボードは、ディスク・ドライブやストリーム入力などのプレーヤ、レコーダに必要な接続が可能になっており、弊社提供のドライバ・ソフトウェアにより各種評価、開発が可能となっています。

## 6. むすび

本稿では、EMMA3の様々な機能の特長を説明しました。本LSIを用いることにより、HD DVDのプレーヤ、レコーダを共通プラット・フォームで構築することが可能です。レコーダにおいては2番組同時録画、1番組再生など高機能かつ低コストなセットが実現可能です。

今後弊社では、引き続き成長が期待される次世代DVDプレーヤ、レコーダおよびその応用機器向けに多様なシステムLSIを継続して投入し、積極的な開発、製品展開を行う計画です。

\*MIPSは米国MIPSテクノロジー社の商標です。

\*LinuxはLinus Torvalds氏の、米国およびその他の国における登録商標あるいは商標です。

\*DTSはデジタル・シアター・システムズ社の登録商標です。

\*DVD、HD DVDはDVD Format/Licensing Corporationの商標です。

\*Dolbyおよびドルビーは、Dolby Laboratories Inc.の登録商標です。

## 執筆者プロフィール

松永 光浩

NECエレクトロニクス

第二SoC事業本部

SoCシステム事業部

下嶋 覚

NECエレクトロニクス

第二SoC事業本部

デジタルコンシューマLSI事業部

五嶋 宏之

NECエレクトロニクス

第二SoC事業本部

SoCソフトウェア事業部

坪井 栄二

NECエレクトロニクス

第二SoC事業本部

デジタルコンシューマLSI事業部

中溝 正樹

NECエレクトロニクス

第二SoC事業本部

SoCソフトウェア事業部