# 新デカップリングデバイス 「プロードライザ」の開発、量産

高橋 健一・井上 武夫・長沢 寿久・関口 芳典

## 要 旨

プロードライザは、数10kHz～数GHzの広い周波数範囲において、低インピーダンスでフラットな周波数特性を持ち、かつ大容量であるという特徴を併せ持つ、現在、および将来の市場要求にマッチした画期的なデカップリングデバイスです。本稿では、プロードライザの特徴、構造、特性、信頼性、量産化およびシリーズ化について解説します。

## キーワード

●大容量 ●低インピーダンス ●高周波 ●デカップリング

## 1. まえがき

近年のエレクトロニクス市場における技術動向は、半導体の高集積化による1チップ化が進展し、部品点数の大幅削減が進んでいます。一方、コンデンサなどの受動部品に関しては、単一機能の枠内での進化にとどまっているため、機能の複合化、および部品点数の削減が急務であるといえます。

このような背景のなか、当社では、広い周波数帯域において低インピーダンス、大容量という特徴を有し、優れたデカップリング機能とノイズキャンセラー機能を併せ持つ新デカップリングデバイス プロードライザの開発、量産に成功しました。

昨年より一部顧客への供給を開始し、デジタル機器などを中心に顧客からの期待も日増しに高まっています。

また、本デバイスは、その斬新さや、高性能が高い評価を受け、日刊工業新聞社 十大新製品(2003年度)、経済産業省第一回ものづくり日本大賞優秀賞、第53回電気科学技術奨励賞(オーム技術賞)などを受賞しています。

本稿では、市場での要求を受けて本格的に量産が始まったプロードライザについて、特徴、構造、特性、量産化、シリーズ化、および信頼性について解説します。

## 2. プロードライザの特徴

プロードライザは、導電性高分子系コンデンサ並みの大容量と、低ESR(等価直列抵抗)、さらにはセラミックコンデンサよりも3桁も低いESL(等価直列インダクタンス)特性を実現し

た、伝送線路構造を有するデバイスであり、100kHz～数GHzオーダーの広い周波数帯域にわたって、低インピーダンスでフラットな周波数特性を有しています。この優れた特性を持つことにより、従来、様々なタイプのコンデンサを多数組み合わせる必要があったデカップリング回路をプロードライザ数個で代替することが可能となり回路設計の簡略化、および部品点数の大幅削減が実現できます。実際に試作したサーバでは、セラミックコンデンサ87個をプロードライザ6個に置き換える、CPUが問題なく動作することを確認しています。

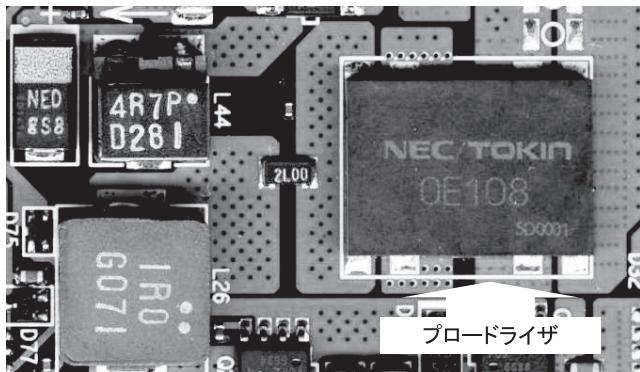

また、この特徴を活かしたプロードライザの採用例としては、NEC製ノートPC「VersaPro UltraLite」「LaVie」への搭載が挙げられます(写真1、写真2)。

この採用例では、積層セラミック、アルミ電解など数十個のコンデンサが、プロードライザ1個に置き換わり、かつCPUの電源電圧変動を同等以上に押さえ込むことに成功しています。

写真1 NEC製ノートPCの外観

### 3. プロードライザの構造

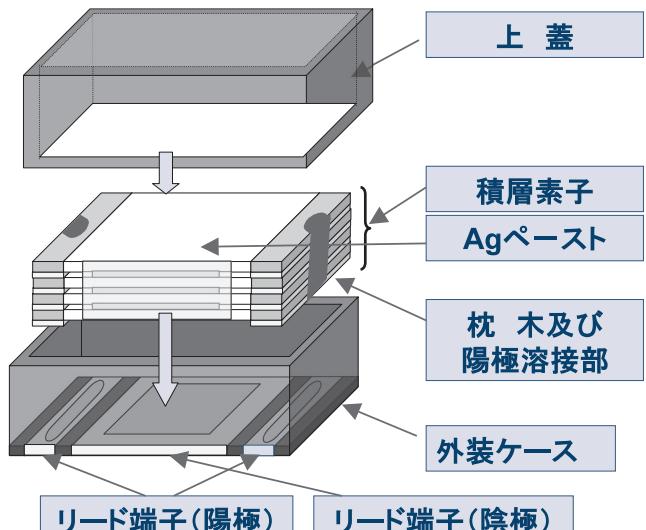

次に、プロードライザの製造方法、および構造の概略を説明します。両面をエッチングし、化成処理により誘電体皮膜を形成させたアルミの化成箔を陽極体とし、この化成箔上に導電性のポリマー層を形成し固体電解質とします。さらにこのポリマー層の上にグラファイト層、銀ペースト層を順次形成し、単層の3端子アルミ電解コンデンサ素子を得ます。

次に、この素子の陽極部に枕木と呼ばれる銅合金の金属片を超音波溶接により接続し、所定の静電容量に見合った枚数の素子を積層します。積層の際、陽極部はレーザ溶接、陰極平面部および側面部は導電性ペーストで接続することで、単層の素子が複数枚重なって接続された積層体を構成します。

一方、外装ケースは、陽極-陰極-陽極の3端子からなるリードフレーム上に熱可塑性樹脂をインサートモールドしたものを使用します。積層体はこのケース内に収められ、それぞれの陽極、陰極部が導電性ペーストでリードフレームの外部端子部に接続され、外装カバーがケース上にエポキシ接着剤で接着された構造となっています(写真3、図1)。

このように、素子にアルミおよびその誘電体を用いることにより、高容量で信頼性が高くかつコストを抑えた設計となっています。さらに外装にケース構造を採用することでリードフレーム実装時の熱ストレスを大幅に緩和でき、インサートモールドにより精度の高い端子設計を実現できました。

### 4. プロードライザの特性

プロードライザは、ポリマーコンデンサ材料技術(大容量、

図1 プロードライザF型(積層品)の構造図

低ESR)、高周波理論に基づく伝送線路構造の採用(低ESL)、NeoCapacitorで培った高信頼度設計技術(高耐熱性)をコア技術として、広い周波数領域にわたるフラットな低インピーダンス特性を実現しています。

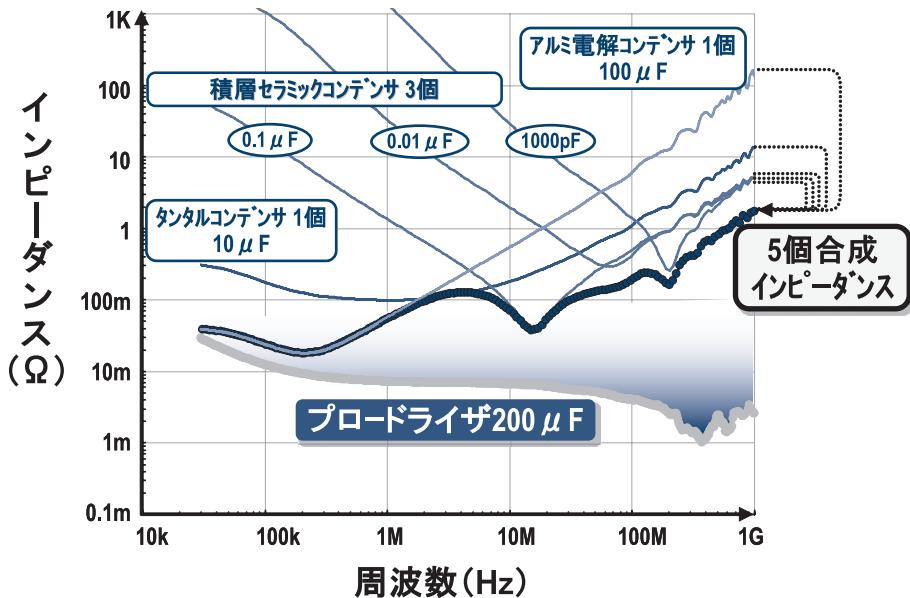

図2はプロードライザのインピーダンス特性(対周波数特性)をアルミ電解コンデンサ、タンタルコンデンサ、積層セラミックコンデンサの測定結果と合わせて示したものです。プロードライザ以外の従来のコンデンサはV字型のインピーダンス特性を示しており、低インピーダンスである周波数領域が自己共振周波数の近傍に限られていることが分かります。

このため、広い周波数帯域で低インピーダンスであることが必要なデカップリング回路を構成するには、自己共振周波数の異なるコンデンサを多数組み合わせる必要があります。

図2 プロードライザ インピーダンスの周波数特性

参考として同じく図2に各コンデンサ5個を並列接続した際の合成インピーダンスを計算により求めたものを示しますが、プロードライザはこの合成インピーダンスと比較してもはるかに低インピーダンスで、かつフラットな周波数特性を示しています。この結果からもプロードライザのデカッピング能力、ノイズ吸収力が、従来の異種コンデンサの組合せよりも優れていることが分かります。

## 5. プロードライザの量産化

プロードライザの量産化は、数多くの課題を解決することにより実現しましたが、本章では特に難易度の高かった低ESR化(100kHz)、陽極積層溶接、およびはんだフィレットについて報告します。

### 5.1 低ESR化

低インピーダンスを実現するためには、高周波帯域でESLを抑えると同時にESRを低減することが必要条件となります。ここでは、低ESR化への取り組みについて解説します。

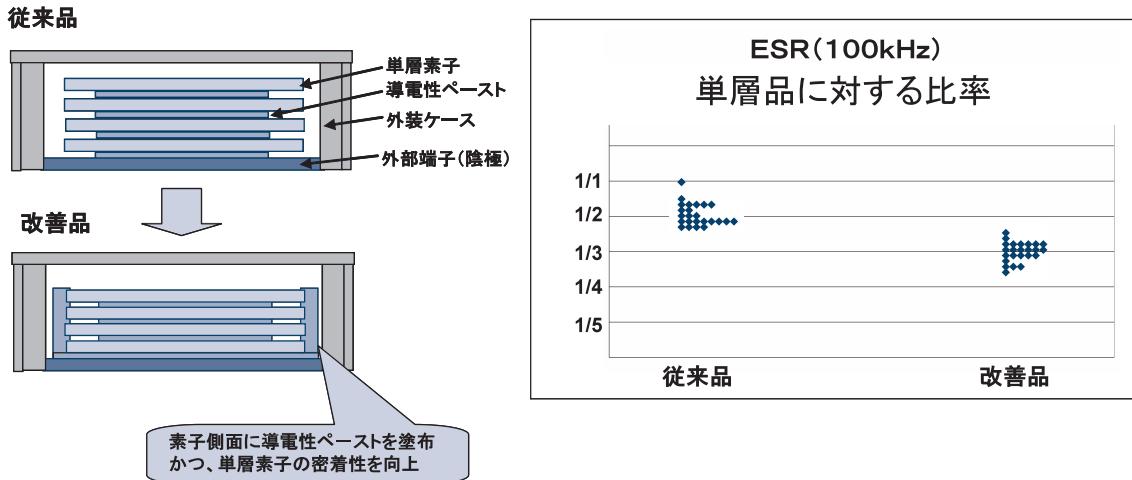

プロードライザでは、単素子当たりのESR値(100kHz)に対し、たとえば4素子を積層したときには、各々が並列接続とな

るので、単素子の1/4の値が4枚積層品のESR(100kHz)理論値となります。しかしながら、量産試作当初のESR(100kHz)の平均値は、4枚積層品の場合、図3のように目標値：単層品の1/3以下に対して、1/2程度でした。

このギャップは、製品の積層体の接続状態、積層体と端子の接続状態および各材料の固有抵抗によるものと考えられます。プロードライザは、前述の3項に示したように、外部端子から上方へ素子を積み重ねる構造を取るため、理論値で計算された目標値を達成するためには、いかに最下層から最上層までの素子を低抵抗で接続させるか、すなわち、並列接続した場合の各素子抵抗を、いかに低くできるかが重要なポイントとなります。

以上の考察により、ESRの低減には外部端子から最上層の素子まで断面積の大きな電流の経路を確保し、外部端子から最上層素子間のトータルの抵抗を下げることが有効と推測されます。

そこで、陰極平面部のみを導電性ペーストで接続していた積層体について、さらに陰極側面にも導電性ペーストを回り込ませて塗布しました。また外部端子から最上層素子にいたるまでの密着性をより向上させるため製造条件の見直しを行いました。

この結果、図3に示すように、4枚積層品でのESR値(100kHz)を、目標値である単層品の約1/3まで低減でき、量産可能な実力を確保しました。

図3 ESR(100kHz)の改善

### 5.2 陽極積層溶接について

積層構造を採用しているプロードライザにおいて、積層された各素子どうしの接続方法の選択は、製品の信頼性を確保する上でも重要なポイントの1つとなります。ここでは陽極部の接続について解説します。

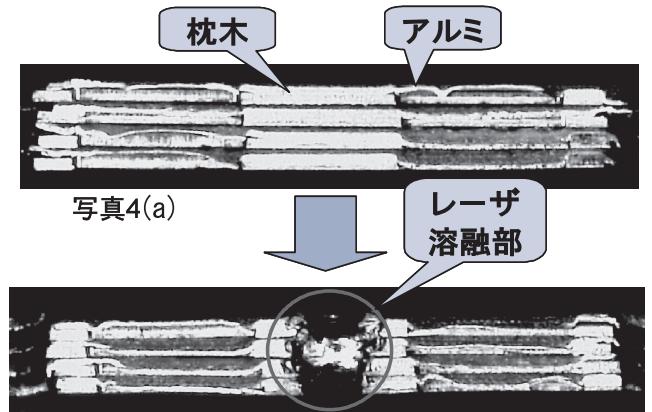

積層された内部素子の陽極部の接続は、溶接工法を選択しました。溶接工法には抵抗溶接、レーザ溶接など何種類かの選択肢がありますが、接続強度、信頼性および量産性を考慮しレーザ溶接を採用しました。また、レーザの種類には、CO<sub>2</sub>、YAG、エキシマなどがありますが、レーザ出力と被溶接物の融点、レーザ波長と溶接エリア、さらに自動機への組み込みの容易さなどを検討した結果、YAGレーザを使用することにしました。特に陽極部を2ヶ所持つ3端子構造のプロードライザの場合、溶接箇所も2ヶ所となるため、レーザ光をファイバーで分岐できるYAGレーザは、量産性、装置コストの面からも最適といえます。

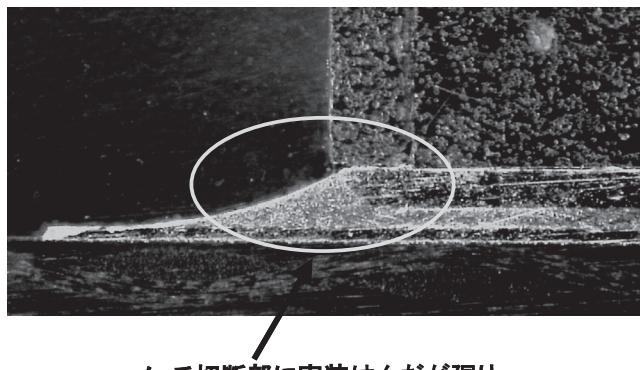

写真4(a)にレーザ溶接前、写真4(b)にレーザ溶接後の外観写真を示します。内部素子陽極部のアルミ、および各素子の枕木どうしがレーザ溶接により完全に溶融している状態が観察されます。また、スパッタなど、溶融物の噴き出しがなく、安定した溶接状態が得られています。

### 5.3 はんだフィレットについて

表面実装型のチップ部品では、基板実装後における端子へ

写真4 レーザ溶接部断面SEM

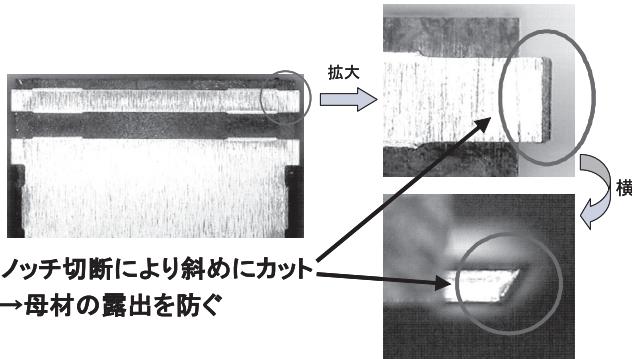

のはんだ回り確認のため、ほとんどの顧客から、実装後の端子にはんだフィレットの形成を要求されます。プロードライザも表面実装型の部品であることから端子切断方法を工夫することによりはんだフィレットの対応をしました。

プロードライザのような下面電極タイプの部品において、はんだフィレットを形成するためには、外部端子の切断面に後めつきを施したり、あらかじめ切断部分に孔やエンボス加工を施しておくのが一般的です。しかし、このような方法は、コストアップにつながるため、プロードライザでは、外部端子の切断時に、まずノッチ加工を施し、さらにそのノッチ部分を切断する方式を採りました(写真5)。この方式によると、ノッ

## エネルギーデバイス

### 新デカッピングデバイス「プロードライザ」の開発、量産

写真5 外部端子 切断外観

ノッチ切断部に実装はんだが廻り

十分にフィレットを形成している

写真6 切断部のはんだフィレット形成状態

チ部にめっきを残し、かつめっきが残らない切断断面は最小にできるので、基板実装時には、ノッチ部にはんだが這い上がり、はんだフィレットを形成します(写真6)。

プロードライザの量産体制に関しては、2006年3月までに国内工場での600万個/月体制を確立しました。引き続き海外工場で400万個/月の生産能力の増強を進めており、合計1,000万個/月までの生産体制を整える計画です。

## 6. シリーズ化(製品ラインナップ)

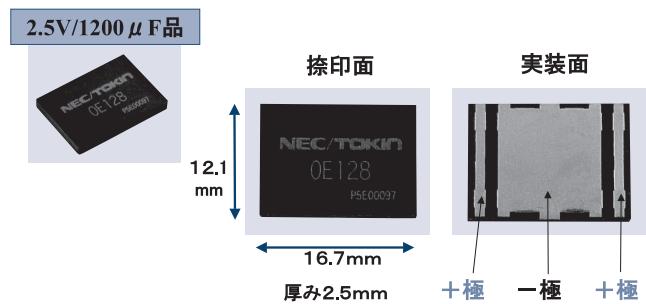

現在プロードライザはFサイズ2.5V/1,000 $\mu$ F、2.5V/1,200 $\mu$ Fを量産しており、引き続き2.5V/1500 $\mu$ Fを開発中です。ともに最新の半導体における低電圧、高周波、大電流化に対応するため、高周波数域でのさらなる低インピーダンス化と大容量化を積極的に進めています(表)。

表 プロードライザの製品ラインナップ

| 型番           | 形状(mm)            | 定格電圧(V) | 静電容量( $\mu$ F) | 状況  |

|--------------|-------------------|---------|----------------|-----|

| PFAF250E108M | 16.7 × 12.1 × 2.5 | 2.5     | 1,000          | 量産中 |

| PFAF250E128M | 16.7 × 12.1 × 2.5 | 2.5     | 1,200          | 量産中 |

| PFAF250E158M | 16.7 × 12.1 × 2.5 | 2.5     | 1,500          | 開発中 |

## 7. 高温信頼性について

プロードライザはCPU周りのデカッピングコンデンサとして使用されるため、CPU周辺の温度上昇に対する信頼性について検証しておく必要があります。

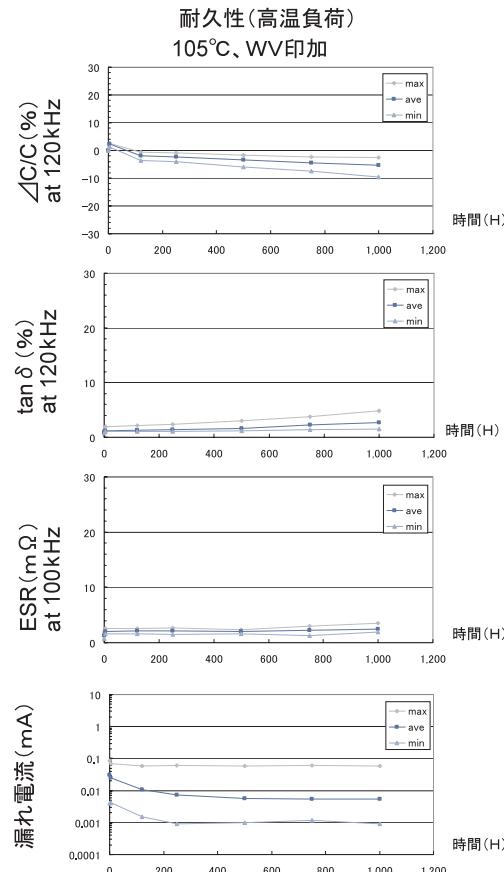

図4は、高温負荷(105°C、2.5V印加)での信頼性データです。105°Cの高温雰囲気中において、1,000Hまで顕著な劣化がないことが分かります。今後、さらなる耐熱性向上のため、工法、材料の両面から改善を進めます。

図4 信頼性試験結果

## 8.まとめ

プロードライザは、デカッピングデバイスとして多くのデジタル機器に対応できる画期的な新デバイスであり、市場においてもその優位性が認められ、一部顧客への供給を開始しました。今後、市場をさらに拡大するためには、小型、大容量化などのシリーズ拡大と低コスト化が必須といえます。

これからも、高性能、低成本を意識した製品をタイムリーにリリースすべく開発、量産に注力し、弊社が提唱している世界初の複合受動部品 Integrated Passive Component(IPC)としてグローバルスタンダード化をめざします。

### 参考文献

- 1) 荒井智次、高橋正彦、戸井田剛、猪井隆之:「伝送線路構造の新デカッピングデバイスの開発とそのアプリケーション」NEC TOKIN Technical Review Vol.30,2003,pp14-20.

- 2) 荒井智次、坪田一成、猪井隆之、堀仁孝:「伝送線路構造デバイス プロードライザTMのノートPCへのアプリケーション」NEC TOKIN Technical Review Vol.32,2005,pp91-96.

### 執筆者プロフィール

高橋 健一

NECトーキン

キャバシタ事業部

製品技術部

井上 武夫

NECトーキン

キャバシタ事業部

CS品質推進部

長沢 寿久

NECトーキン

キャバシタ事業部

製品技術部

マネージャー

関口 芳典

NECトーキン

キャバシタ事業部

CS品質推進部

マネージャー

●本論文に関する詳細は下記をご覧ください。

関連URL: [http://www.nec-tokin.com/product/

proadlizer/index.html](http://www.nec-tokin.com/product/proadlizer/index.html)

[http://www.nec-tokin.com/product/

pdf\\_dl/proadlizer\\_j.pdf](http://www.nec-tokin.com/product/pdf_dl/proadlizer_j.pdf)