# SX-8 の実装技術

## Packaging Technology for SX-8

田中慎二\*

Shinji Tanaka

高橋 勲\*

Isao Takahashi

浜口博幸\*

Hiroyuki Hamaguchi

名取正樹\*\*

Masaki Natori

筑木博之\*

Hiroyuki Tsuzuki

永田哲也\*\*\*

Tetsuya Nagata

### 要旨

本稿では、SX-8の実装技術の概要について述べます。

SX-8では、世界最高性能、高いコストパフォーマンス、優れた設置性を実現するために前機種（SX-6）で実現したワンチッププロセッサをさらに進化させ、その性能を最大限に引き出すために高密度LSI実装技術、高密度接続技術、高効率冷却技術、高性能電源モジュールを採用しました。また、これらの特徴を最大限アピールする先進的なデザインを採用しています。

This paper describes the packaging technology used in the supercomputer SX-8.

The SX-8 has achieved superior cost-performance and minimizing the installation areas by high density LSI packaging, high density interconnect technology, high-efficiency cooling system and high-performance power supplies.

### 1. まえがき

スーパーコンピュータSXシリーズの特徴は、すべてのCPU（Central Processor Unit）が1つのノード内においてすべてのメモリ空間を共有する点（共有メモリ方式）と、システム全般を高速動作させるために実装全般にわたって高速化が要求される点にあります。これらの仕様を実現するために開発した実装技術と、デザインについて以下に紹介します。

### 2. 高密度実装技術

超高速動作が要求されるCPU/MMU（Main Memory Unit）モジュールは、SX-6で採用した高密度実装をさらに進化させて大型で多ピンのLSIを搭載可能としています。

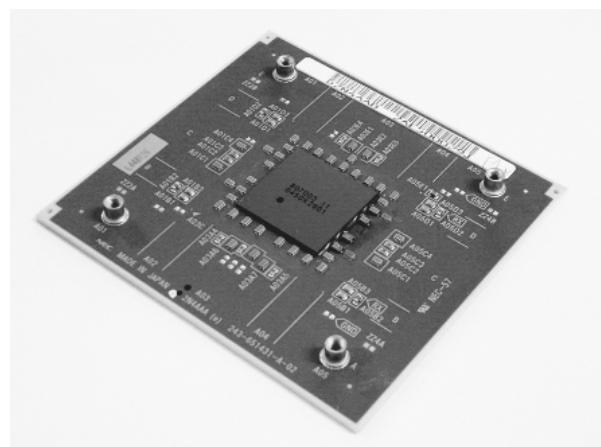

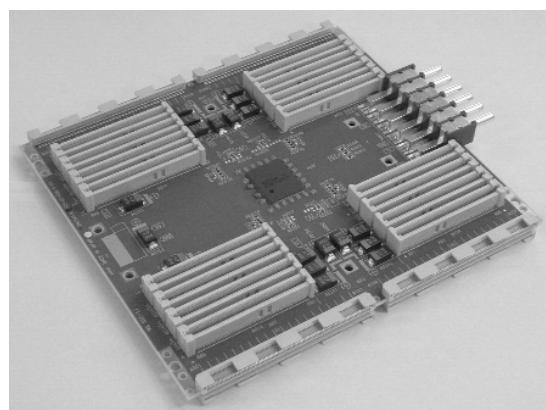

CPU/MMUモジュールの外観を写真1、写真2に示します。

CPUモジュールは、CPU LSIをビルトアップ基板表面に

写真1 CPUモジュールの外観

Photo 1 External view of CPU module.

写真2 MMUモジュールの外観

Photo 2 External view of MMU module.

\* コンピュータ事業部

Computers Division

\*\* NECコンピュータテクノ

NEC Computertechno, Ltd.

\*\*\* NECデザイン

NEC Design, Ltd.

表1 CPU/MMU モジュールの諸元

Table 1 Specifications of CPU/MMU module.

| 項目                      | CPUモジュール                                                                                  | MMUモジュール                                                                               |

|-------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 搭載LSI (形態)              | CPU LSI×1<br>(ペアチップ)                                                                      | MMC LSI×1<br>(ペアチップ)                                                                   |

| ピン数                     | 8,210                                                                                     | 5,284                                                                                  |

| IOピッチ ( $\mu\text{m}$ ) | 182                                                                                       | 182                                                                                    |

| 搭載RAM                   | -                                                                                         | $\mu\text{BGA} \times 96$                                                              |

| 配線基板                    | 種類<br>基板サイズ (mm)<br>基板厚 (mm)<br>基板層数<br>配線密度 ( $\mu\text{m}$ )<br>via仕様 ( $\mu\text{m}$ ) | ビルドアッププリント配線基板<br>85×75<br>1.8<br>5ビルド-8コア-5ビルド<br>配線幅/間隙 = 20/20<br>via径/ランド径 = 50/80 |

| モジュール                   | 入出力端子数<br>冷却<br>消費電力 (W)                                                                  | 5,329<br>空冷<br>75                                                                      |

|                         |                                                                                           | 824                                                                                    |

ペアチップ実装し、裏面には入出力用のLGA (Land Grid Array) PADが形成されています。MMUモジュールは、メモリ制御用のMMC LSIとメモリキャリア用コネクタをビルドアップ基板表面に実装しています。CPU/MMUモジュールの諸元を表1に示します。

## 2.1 LSI 実装技術

LSIの性能を最大限に引き出すために、SX-6と同様にペアチップ実装を採用しています。LSIには鉛フリーはんだバンプが形成されており、ビルドアップ基板に形成されたパッドと鉛フリーはんだで接続されます。そして、LSIと基板間にアンダーフィル樹脂が充填されます。

狭ピッチはんだ供給技術、接続技術、洗浄技術、樹脂充填技術の改善により、SX-6よりIOピン数の増大 (5,185→8,210) 並びに狭ピッチ化 ( $200\ \mu\text{m}$ → $182\ \mu\text{m}$ ) を達成しています。

## 2.2 配線基板技術

### (1) 微細ビルドアップ基板

アディティブ工法によるパターン形成、レーザ工法によるヴィア形成により、配線ピッチ  $40\ \mu\text{m}$  (配線幅/間隙 =  $20/20\ \mu\text{m}$ ) という微細化を実現しています。また、ビルドアップ層を表裏各5層形成することで8,000を超えるペアチップのIO端子を受け、全信号をファンアウトすることができます。

### (2) 高多層プリント基板 (ノードボード)

電気特性のすぐれた最先端材料 (比誘電率 = 3.5, 誘電正接 = 0.005) を採用した高多層プリント基板 (38層板) の開発により、3Gビット毎秒という高速信号伝送を実現しました。また、CPUモジュールとMMUモジュールの各信号ピンアサインを最適化することで配線収容性を向上させ、信号層19層での総配線長は約2.7kmになります。ノードボードの諸元を表2に示します。

表2 ノードボードの諸元

Table 2 Specifications of node board.

| 項目                     | ノードボード                                  |

|------------------------|-----------------------------------------|

| サイズ (mm)               | 510(W) × 460(D) × 5.8(H)                |

| 材料                     | 低誘電正接材                                  |

| 層数                     | 38層 (信号19層)                             |

| 配線密度                   | 2本/mm                                   |

| 配線仕様 ( $\mu\text{m}$ ) | 配線幅/間隙 = 70/75                          |

| 実装デバイス                 | CPUモジュール×4<br>RCUモジュール×1<br>MMUモジュール×32 |

## 2.3 鉛フリーはんだ実用化技術

SX-8は、ペアチップ接続部を含むすべてのはんだ付け部に鉛フリーはんだ (Sn-Ag-Cu系) を適用しています。鉛フリーはんだ適用に際しては、不活性液の飽和蒸気を利用したVPS (Vapor Phase Soldering) 方式により、最高230°CというSn-Ag-Cu系はんだとしては温度の低いプロセスを実現し、部品並びにプリント基板への熱ストレスを抑えるとともに、フローはんだ時の再加熱剥離防止対策、基板ランドの銅食われ対策、プリント基板への信頼性確保設計の盛り込みなどにより製造品質、信頼性を確保しています。

## 3. システム実装技術

### 3.1 ノードユニットの構造

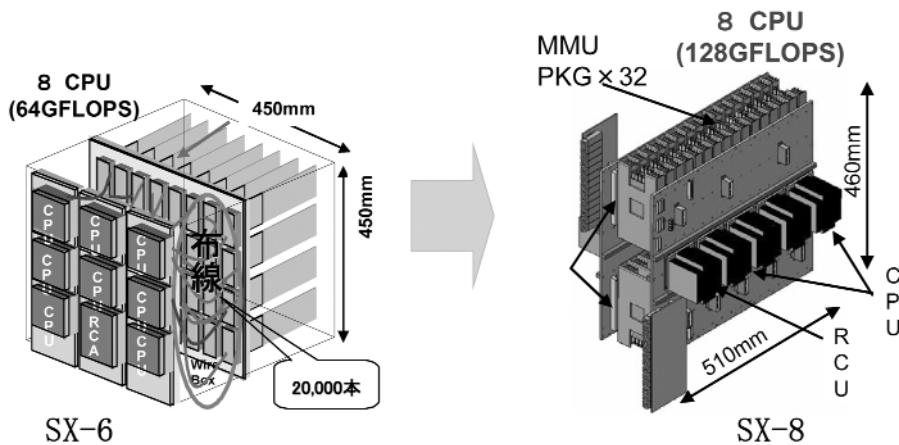

SX-6ではCPUモジュールとMMUモジュール間は約20,000本のケーブルで相互接続されていました。SX-8では、ノードボードと呼ばれるメインのボードを介して、CPUモジュールとMMUモジュールを相互接続するケーブルレス構造を採用しました。図1にSX-6との実装構造の比較を示します。これにより下記の利点を得ることができました。

- ① 1ノードの実装密度はSX-6比で2.5倍の改善

- ② ケーブルレスによる製造工数の低減、並びに誤接続による後戻り工数を低減

- ③ 部品点数の削減によりコストを低減

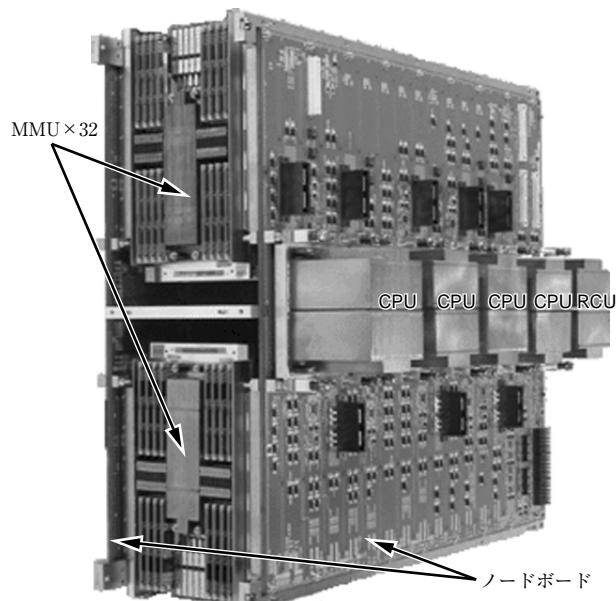

ノードユニットは写真3のように、2枚のノードボードを向かい合わせ、その間にMMUモジュールを32枚挟みます。CPUモジュール4個、RCU (Remote access Control Unit) モジュール1個を、MMUモジュールとは逆面に実装します。これにより1ノードを構成しコンパクトなノードユニットを実現しました。

### 3.2 CPUモジュールの実装技術

CPUモジュールとノードボードの接続にはLGAソケットを使用しています。このソケットの特徴は、以下のとおりです。

- ① 接続芯数は5,329、配列は1 mmの正方格子状と多ピン・高密度化に対応しています。

- ② 接点部にゴム状の弾性体を用いることで、従来のLGAソケットに比べ、接圧が約1/10~1/7という低接圧を

図1 SX-6とSX-8の実装構造比較

Fig.1 Comparison of packaging structure between SX-6 and SX-8.

写真3 ノードユニット

Photo 3 Node unit.

実現しました。従来は1芯当たり約0.3~0.4Nの力を必要としていましたが、このソケットは1芯当たり約0.04Nの力、トータル約200Nで安定した接触を保っています。

### 3.3 MMUモジュールの実装技術

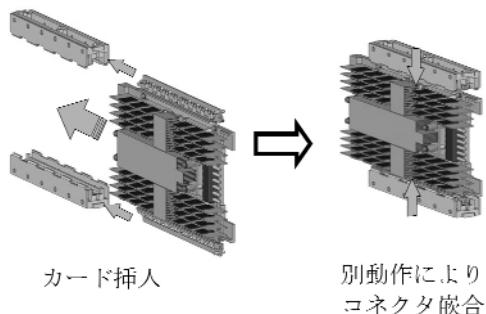

MMUモジュールはノードボードに対して垂直に実装される接続になっています。従来のコネクタは、カードの挿入方向とコネクタの嵌合方向が同じであるため、向かい合う2枚のノードボードの両方に多数のMMUモジュールを接続することは非常に困難でした。そのため、MMUモジュール挿入後に別動作でコネクタの嵌合を行う特殊なコネクタを開発し、MMUモジュールの基板の両端面が、それぞれ向かい合うノードボードと容易に接続できるようにしました。このコネクタの主な特徴は、以下のとおりです。

図2 MMUモジュール用コネクタ

Fig.2 Connector for MMU module.

- ① ZIF (Zero Insertion Force) コネクタで、モジュール挿入後に別動作でコネクタを嵌合させます。図2にMMUモジュールの挿入と勘合の動作を示します。

- ② 極数はMMUモジュール当たりで412芯です。

- ③ ノードボード側コネクタ、MMUカード側コネクタ共にSMT (Surface Mount Technology) 実装です。

- ④ 各極とも電気経路が均一で特性インピーダンスも50Ωで整合しています。

- ⑤ 対向する2枚のノードボードの寸法公差を吸収できる構造になっています。

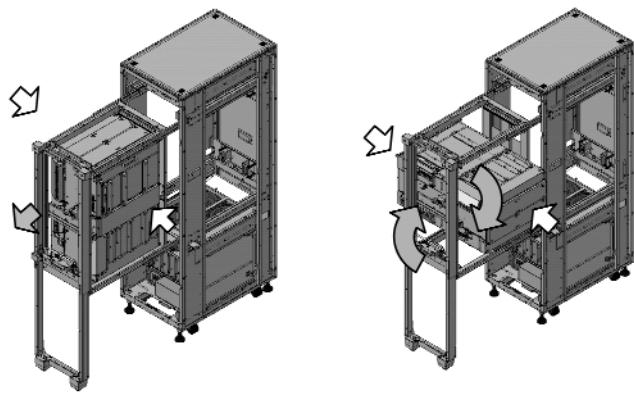

### 4. 筐体技術

写真3で示した挟み込み構造のノードユニットを、そのまま筐体内に実装するとCPUモジュール、MMUモジュールを保守する際に、4方向からのアクセスが必要となります。しかし、装置の4面を保守面として確保することは、装置の設置性を著しく損ないます。そこでSX-8では、図3(a)に示すようにノードユニットを装置の外側にいったん引き出し、この状態で、ノードユニット表面に実装されたCPUモジュールの保守を可能としています。さらに図3(b)

(a) ノードユニット引き出し状態 (b) ノードユニット回転状態

図3 ノードユニットの構造

Fig.3 Node unit structure.

表3 設置面積比較表

Table 3 Comparison of installation areas.

| 項目               | SX-8Aモデル          | SX-6Aモデル          |

|------------------|-------------------|-------------------|

| ピーク性能            | 128GFLOPS         | 64GFLOPS          |

| 設置面積<br>(突起部除く)  | 0.7m <sup>2</sup> | 1.1m <sup>2</sup> |

| 設置面積<br>(保守エリア込) | 1.4m <sup>2</sup> | 2.7m <sup>2</sup> |

に示すようにノードユニットを回転させることで、ノードボード間に挟まれているMMUモジュールの保守を可能にしました。この構造により、4方向のアクセスを可能にしながら、装置としては1面のみのアクセスによる保守を実現しています。その結果、表3のように、装置の小型化だけではなく、保守エリアを含めた設置面積の縮小を実現し、SX-6比で約1/2の小型化を実現しました。保守面を1面にすることができたことで、背中合わせでの設置が可能となり、大規模システムでの設置性改善にも貢献しています。

## 5. 冷却技術

SX-8では、ノードボードの挟み込み実装構造により、CPUモジュールやMMUモジュールなどのモジュールが従来機よりも高密度に実装されており、発熱密度が向上しています。そのため、熱流体シミュレーションによる最適冷却設計を実施しました。

### 5.1 CPUの冷却

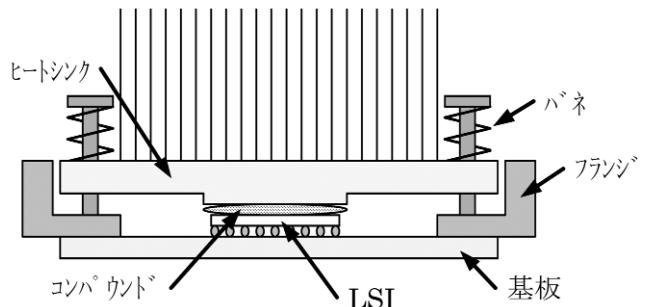

75Wの発熱量を持つCPU LSIの発熱密度は、 $20\text{W/cm}^2$ にもなります。このような高い発熱密度であっても、長期間の運用に耐えられる安定性と信頼性を保証するため、新たな冷却構造を採用しました。

図4にヒートシンクを付けたCPUモジュールの断面図を示します。LSIとヒートシンクの間の微小ギャップには高熱伝導性のシリコンコンパウンドが充填されています。ヒートシンクは熱伝達率、放熱面積、フィン効率、通風抵抗

図4 ヒートシンクを付けたCPUモジュール断面図

Fig.4 Cross section of CPU module with heat sink.

がそれぞれ最適となるように、熱流体シミュレーションによってフィン厚とフィンピッチが決定されています。さらにヒートシンクは、バネによりLSIに押し付けられており、LSIの反りや傾きにも追随してシリコンコンパウンドを押し潰す構造になっています。この構造によって構成部材の寸法バラツキによるコンパウンドの厚みへの影響を最小限に抑え、風速3m毎秒で熱抵抗0.4W/°Cの低熱抵抗構造を実現しています。

### 5.2 装置の冷却

前述したノードユニットの構造上、CPUモジュールとMMUモジュールが接近して実装されているために、冷却条件が異なるモジュールを同じFANで冷却する必要が生じました。そこで、各モジュールに必要な風が行きわたるよう、FANとモジュールの間に風量分配構造を設けて、最適な風量を得られる構造としています。さらに、SX-8は温度可変則ファンを採用することで、マシンの設置環境に合わせて最適なFANの回転数を選択し、低騒音化、低電力化を図っています。また、雰囲気空調にも対応でき設置環境性も優れています。

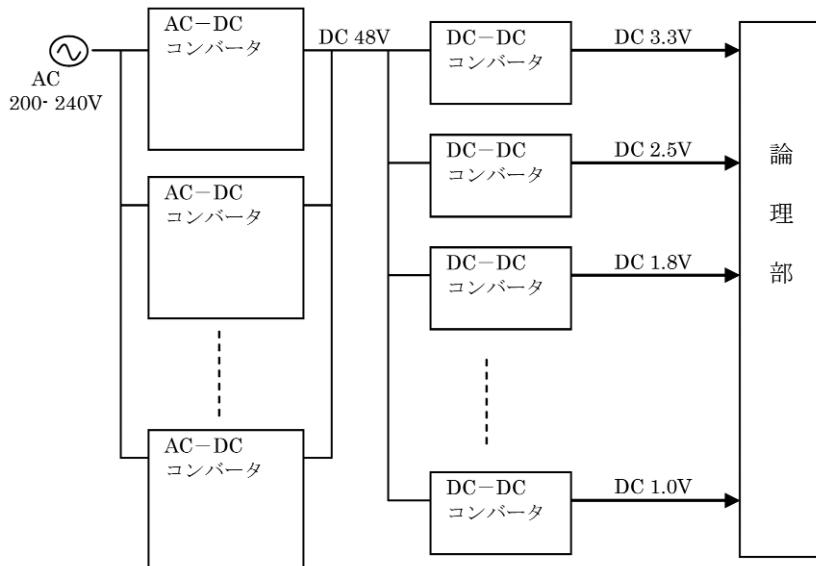

## 6. 電源技術

SX-8の電源システムは、SX-6を踏襲し、48V分散給電方式を採用しています。電源システムの構成を図5に示します。

AC200～240VをAC-DCコンバータで受電しDC48VをDC-DCコンバータに分配しています。AC-DCコンバータを複数台で並列冗長運転することにより、高信頼度の電源システムを実現しました。

DC-DCコンバータはDC48VをDC1.0～3.3Vに変換し、論理部に供給しています。1.0Vの超低電圧を大電流で論理部に供給する必要があるため、給電系の電圧ドロップ、負荷変動による電圧変動を抑えることが課題となっていました。そこで、DC-DCコンバータをノードボードやMMUモジュールに直接コネクタ接続することにより、給電インピーダンスおよびインダクタンス成分の発生を抑え、これを解決しています。CPUモジュール用DC-DCコンバータを写真4に示します。急激な電流変動に追従できるよう、SX-6の2倍の応答速度26μ秒を実現しました。また、出力定

図5 電源システム構成

Fig.5 Block diagram of power supply system.

写真4 CPU用DC-DCコンバータの外観

Photo 4 External view of DC-DC converter for CPU.

写真5 SX-8の外観

Photo 5 External view of SX-8.

格1.0V/120A, 効率83%, 外形200(W)×75(D)×20(H)mmの高密度実装を実現しています。

## 7. デザイン

SX-8では画期的な内部構造や様々な工夫により、最高性能の演算処理能力を非常にコンパクトな筐体に収めることに成功しています。デザインにおいては、このSX-8独自の魅力を最大限アピールすることを考慮しながら進められました。

コンパクトかつフレキシビリティに富むSX-6の流れをさらに推し進めた新構造は、保守面を一方に集約し壁際設置も可能となりました。SX-8のデザインにおいては、その特性を生かすために、全体の造形では装飾を廃したシンプルなデザインとしました。そして筐体カラーにはモノトーンのノアール・ブラックカラーを採用し、様々なシチュエー

ションにおいても環境にマッチするよう配慮されています（写真5参照）。

従来、スーパーコンピュータの超演算処理能力をハードとして、目に見える形で表現することは非常に困難でした。今回、SX-8のデザインにおいては、ソフトウェアの概念も取り入れた新しい手法によって、この製品の真の魅力を引き出すことができたと思います。

## 8. むすび

以上、SX-8の実装技術とデザインについて紹介しました。なおSX-8は、NECが定めた環境配慮基準、およびグリーン購入法に適合した環境配慮型コンピュータとなっていることも特長です。

これからも高い性能と信頼性を備え、コストパフォーマンスに優れたスーパーコンピュータを開発し社会に貢献することがNECに課せられた使命と考えています。今後も、実装技術力向上に努め、魅力ある製品の開発に貢献していく所存です。

### 筆者紹介

Shinji Tanaka

たなか しんじ

**田中 慎二** 1991年、NEC入社。現在、第一コンピュータ事業本部コンピュータ事業部実装技術部エキスパート。

Hiroyuki Hamaguchi

はまぐち ひろゆき

**浜口 博幸** 1980年、NEC入社。現在、第一コンピュータ事業本部コンピュータ事業部実装技術部マネージャー。

Hiroyuki Tsuzuki

つづき ひろゆき

**筑木 博之** 1989年、NEC入社。現在、第一コンピュータ事業本部コンピュータ事業部実装技術部エキスパート。

Isao Takahashi

たかはし いさお

**高橋 熊** 1993年、NEC入社。現在、第一コンピュータ事業本部コンピュータ事業部実装技術部主任。

Masaki Natori

なとり まさき

**名取 正樹** 1990年、NEC甲府入社。現在、NECコンピュータテクノ コンピュータ共通技術部主任。

Tetsuya Nagata

ながた てつや

**永田 哲也** 1983年、NECデザイン入社。現在、デザイングループ1 チーフデザイナー。