東北大

NEC

~待機電力ゼロのキャッシュメモリ実現へ向けて~

電子の**電荷**と**スピン**を利用した**低電力LSI**の開発・実証

# 待機電力ゼロの ロジック混載用高速高集積不揮発性メモリの開発

2013年6月10日

東北大学 省エネルギー・スピントロニクス集積化システムセンター

本成果は、内閣府の最先端研究開発支援プログラム「省エネルギー・スピントロニクス論理集積回路の研究開発」(PL:大野英男教授)により得られたものです。

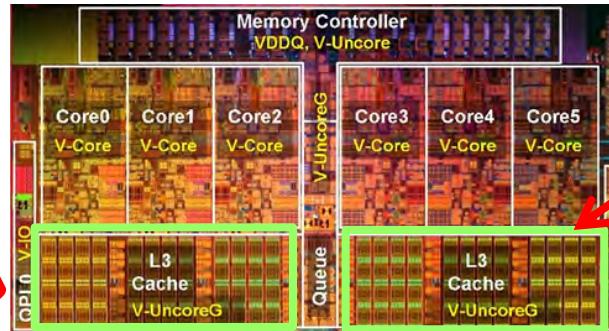

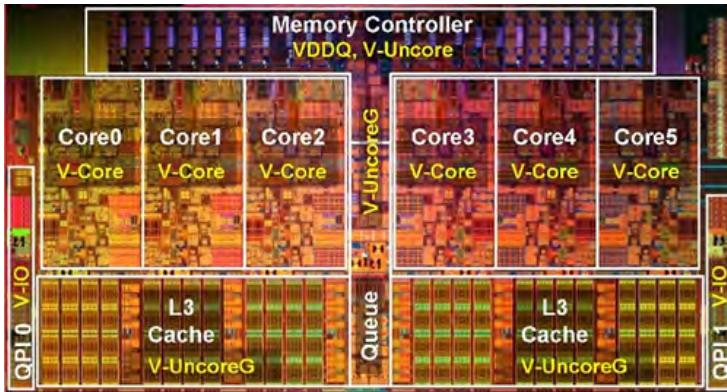

第三階層目の

L3Cacheメモリ

Intel社製 Core i7-980X Extreme

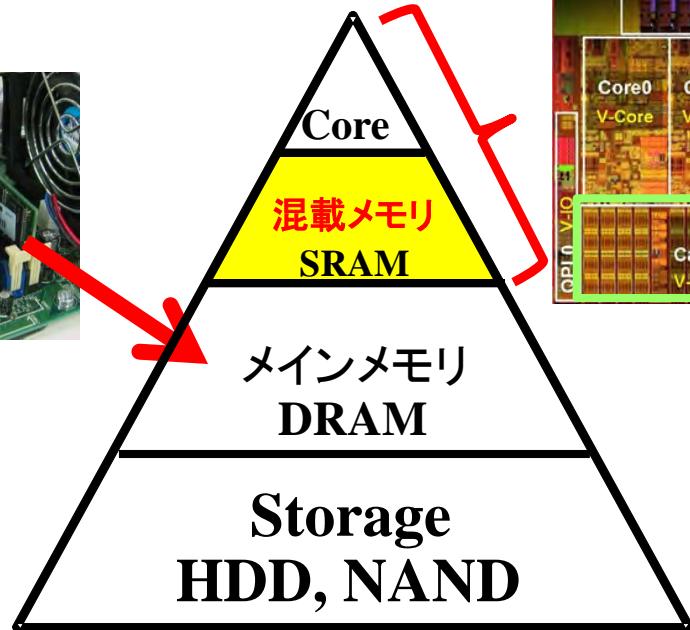

### ＜混載メモリの役割＞

演算処理に必要な大量データを、演算回路

と同一チップ内に保持

### ＜混載メモリへの要求＞

高速演算処理と低消費電力化の両立を実現

|         | メインメモリ | 混載メモリ    |

|---------|--------|----------|

| 容量      | ○(大容量) | △(中容量)   |

| 価格      | ○(安価)  | ×(高価)    |

| アクセス速度  | ×(中速)  | ○(高速)    |

| データ転送速度 | ×(遅い)  | ○(高速)    |

| データ転送電力 | ×(大)   | ○(低消費電力) |

| 待機電力    | ×(大)   | ×(大)     |

### ＜混載メモリの課題＞

マルチコア化に伴い、混載メモリの大容量化が進む。

⇒電源が切れない揮発性メモリであるために、待機電力の増大が大きな課題。

# 不揮発性メモリの性能比較

NANDメモリ 抵抗変化型メモリ 相変化型メモリ

磁気トンネル

接合素子 (MTJ)

書き換え電流

書き換え時間

読み出し時間

データ保持時間

書き換え回数耐性

ロジック混載メモリに要求される高速動作性能と、

書き換え回数耐性( $10^{15}$ 回以上)を考慮すれば、

MTJが現在では唯一の候補

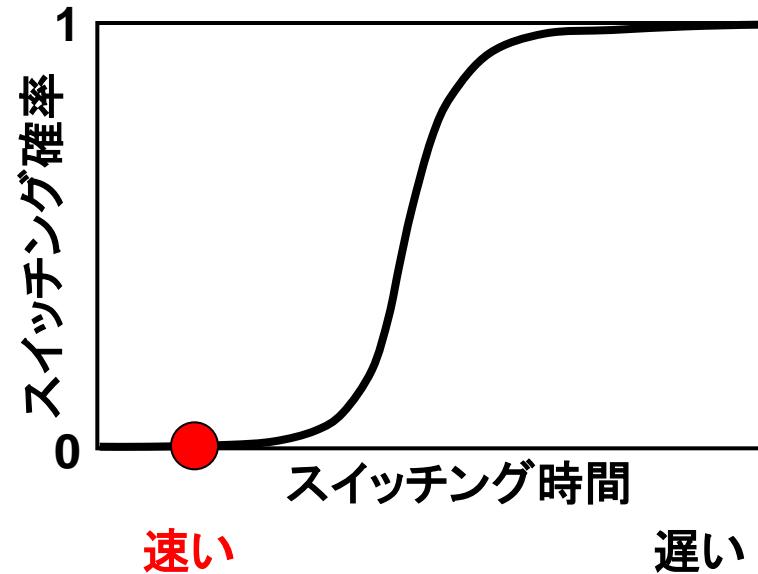

# MTJスイッチング特性

MTJのスイッチング特性によると、高速にスイッチングさせようとすれば、大きな電流が必要になると同時に、スイッチングする確率も減少する。

小さなトランジスタ

MTJを高速にスイッチするのに必要な大電流を

流せない

大容量メモリとして搭載できる小さなセルにおいては、

高速にMTJをスイッチさせることが難しかった。

混載メモリに要求される高速な書き込みサイクルが実現できなかった

この課題を解決して、

キャッシュなどの高速書

込み仕様に対応したMTJ

不揮発メモリを実現する

ことが今回の目的である。

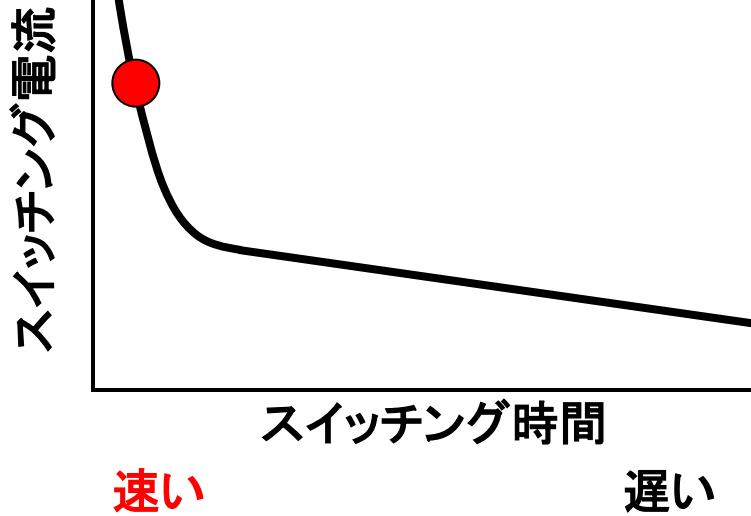

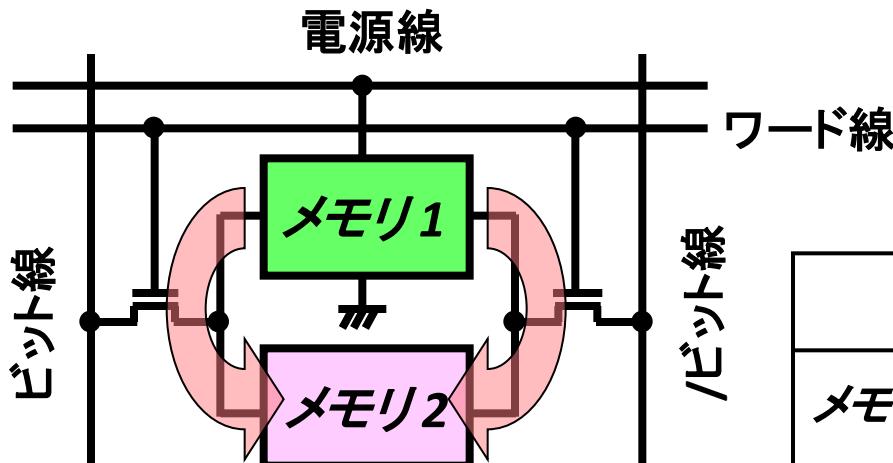

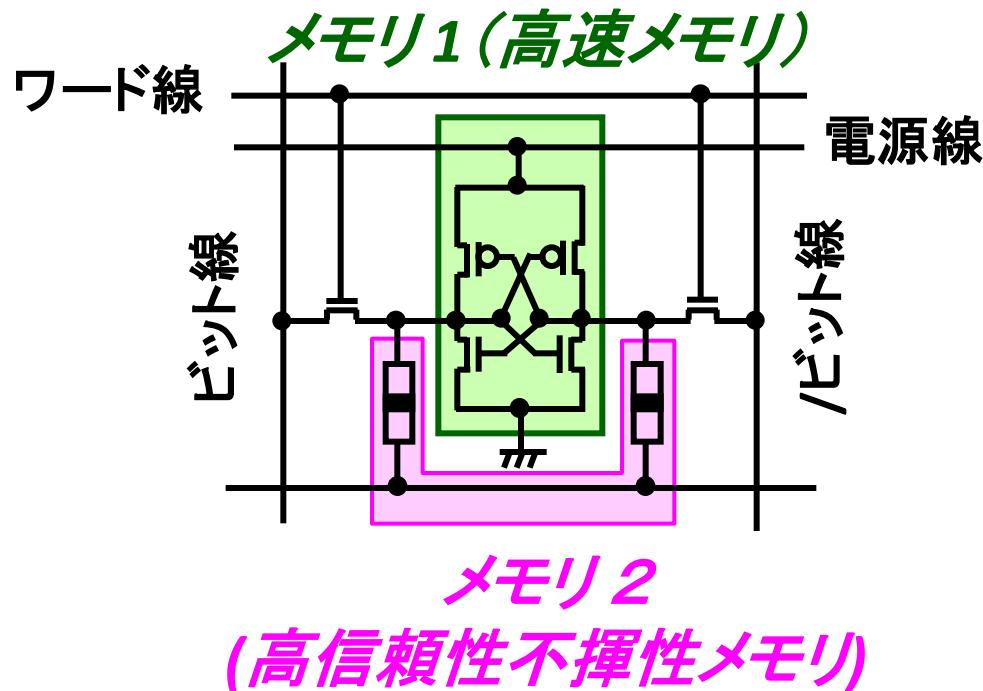

特性の異なる2種類のメモリ

を並列接続させる

|      | 書き込み時間 | データ保持時間 |

|------|--------|---------|

| メモリ1 | 速い     | 短い      |

| メモリ2 | 遅い     | 長い(10年) |

書き込み動作が短時間で終了した場合には、

メモリ1のデータを使ってメモリ2をゆっくり書き換える

(スイッチする)方式を提案。

MTJスイッチングの遅さを外部からは

見えないように隠す回路技術

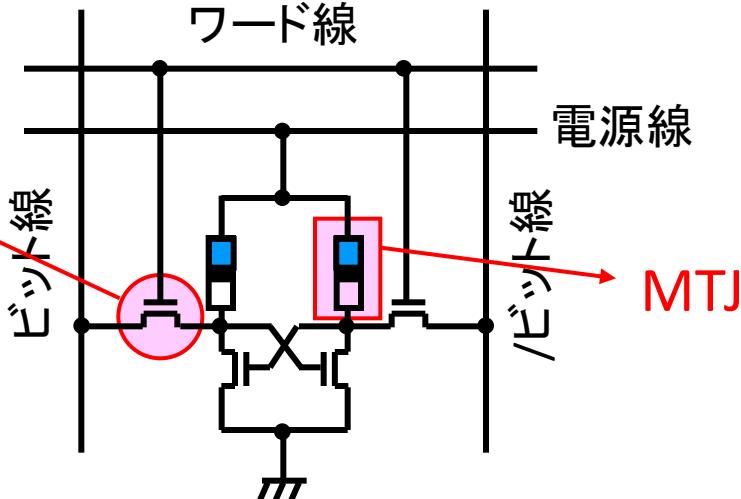

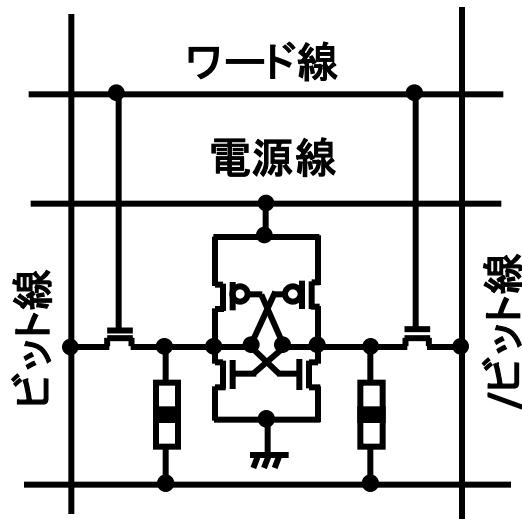

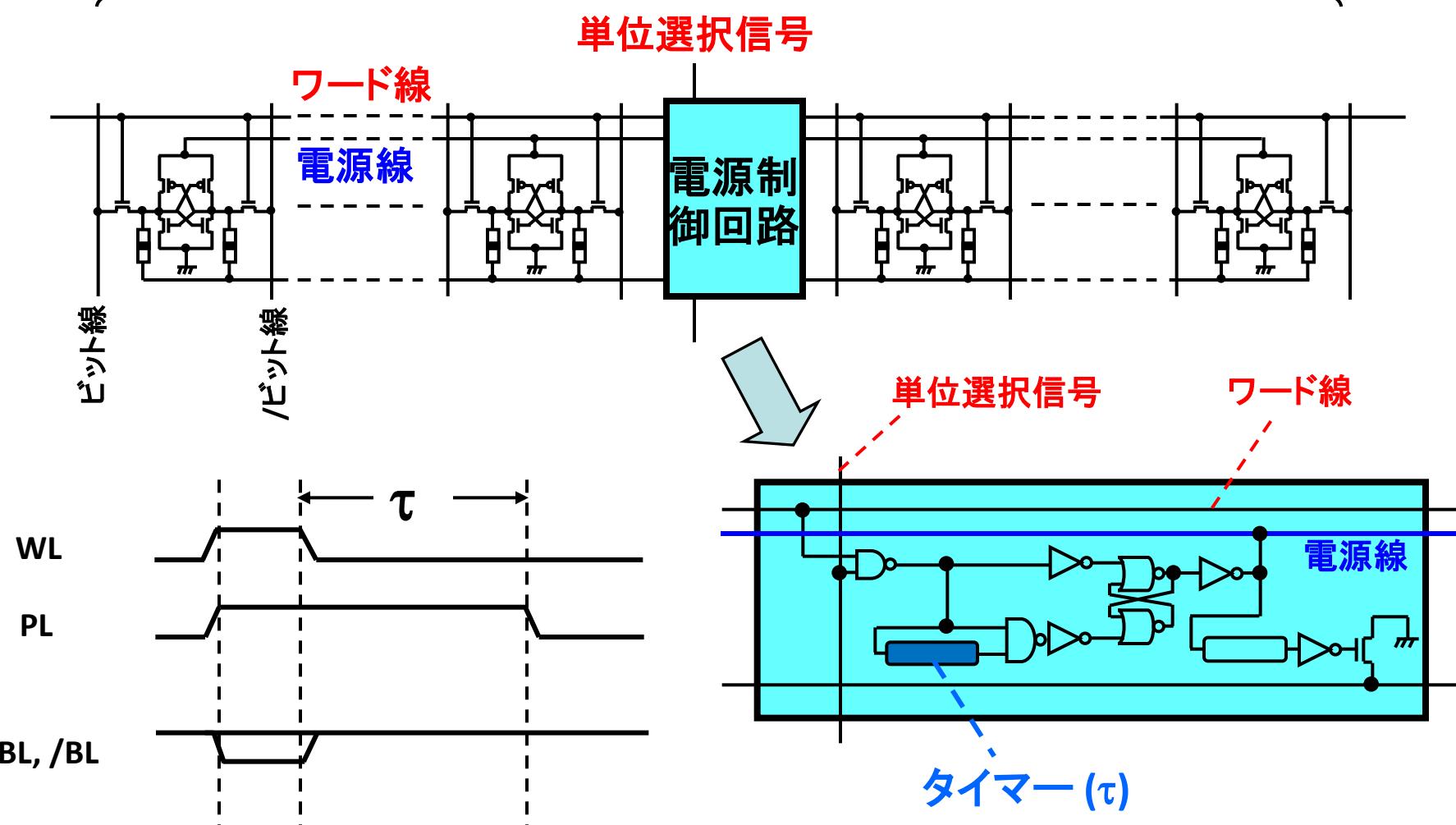

メモリ1としてSRAMを、メモリ2としてMTJ対を採用することで、高速書き込み可能な不揮発性メモリセルを実現することが可能

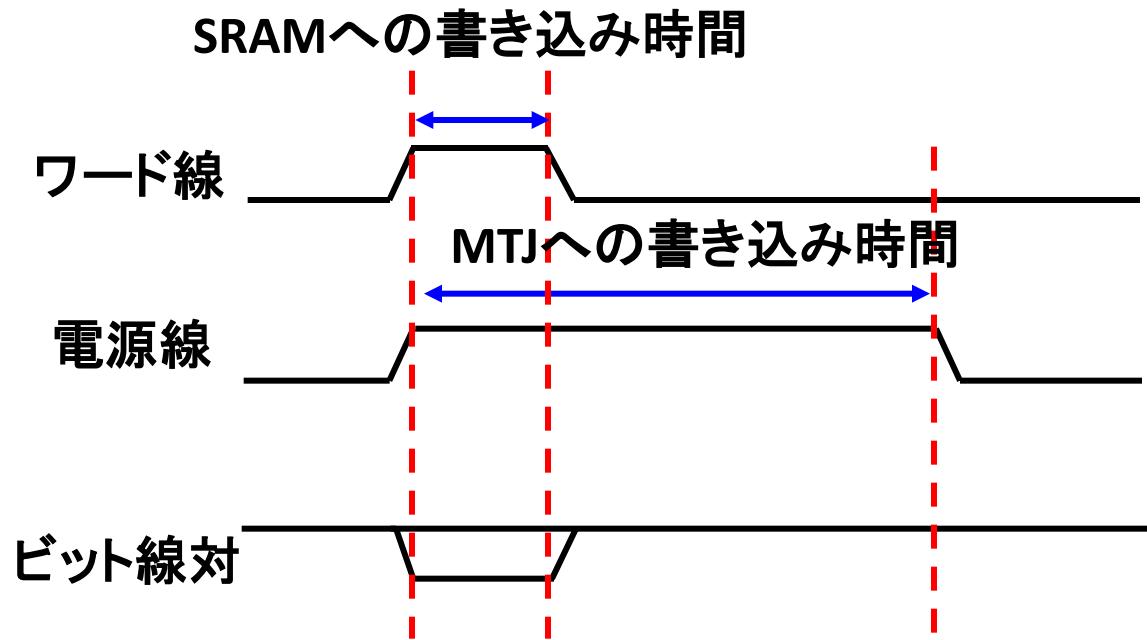

MTJのスイッチが完了したら、電源線の電圧を落として、無駄なパワーをゼロにする。

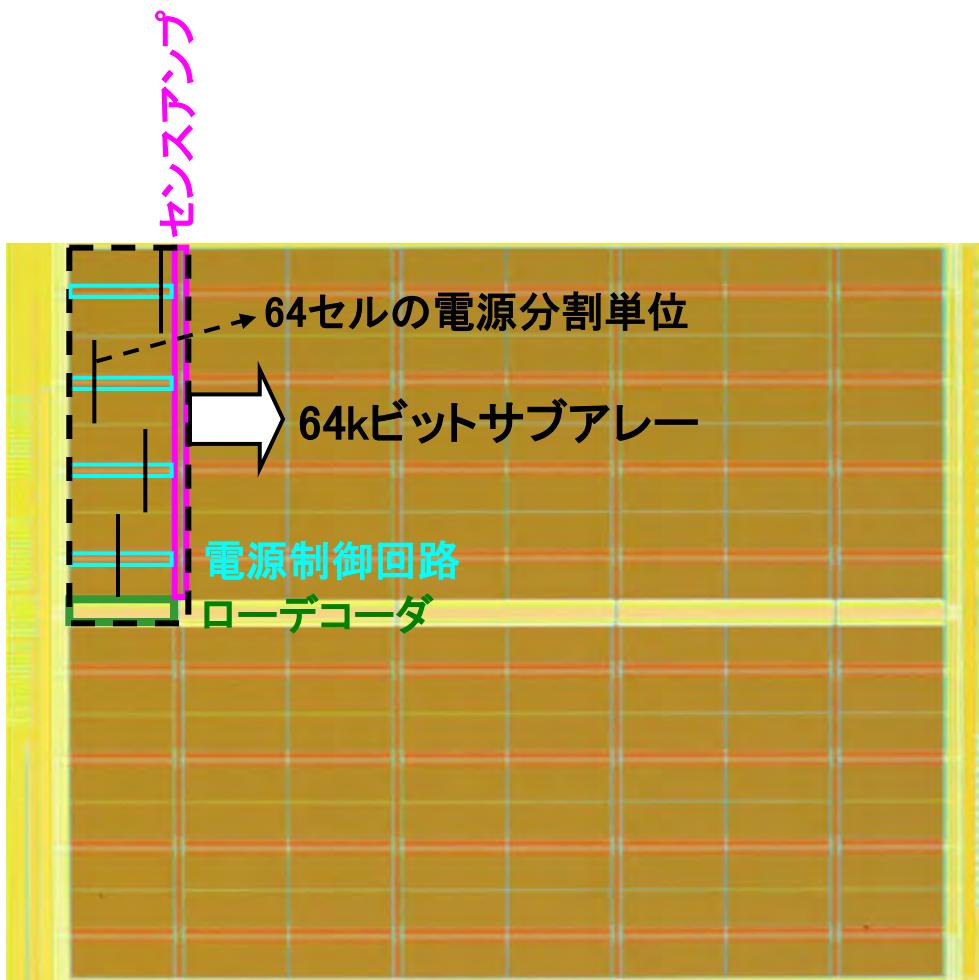

MTJの書き込み終了時間を計測する

タイマーを電源制御回路に搭載

# 電源分割単位毎にタイマー回路搭載

電源分割単位 (64個のセル)

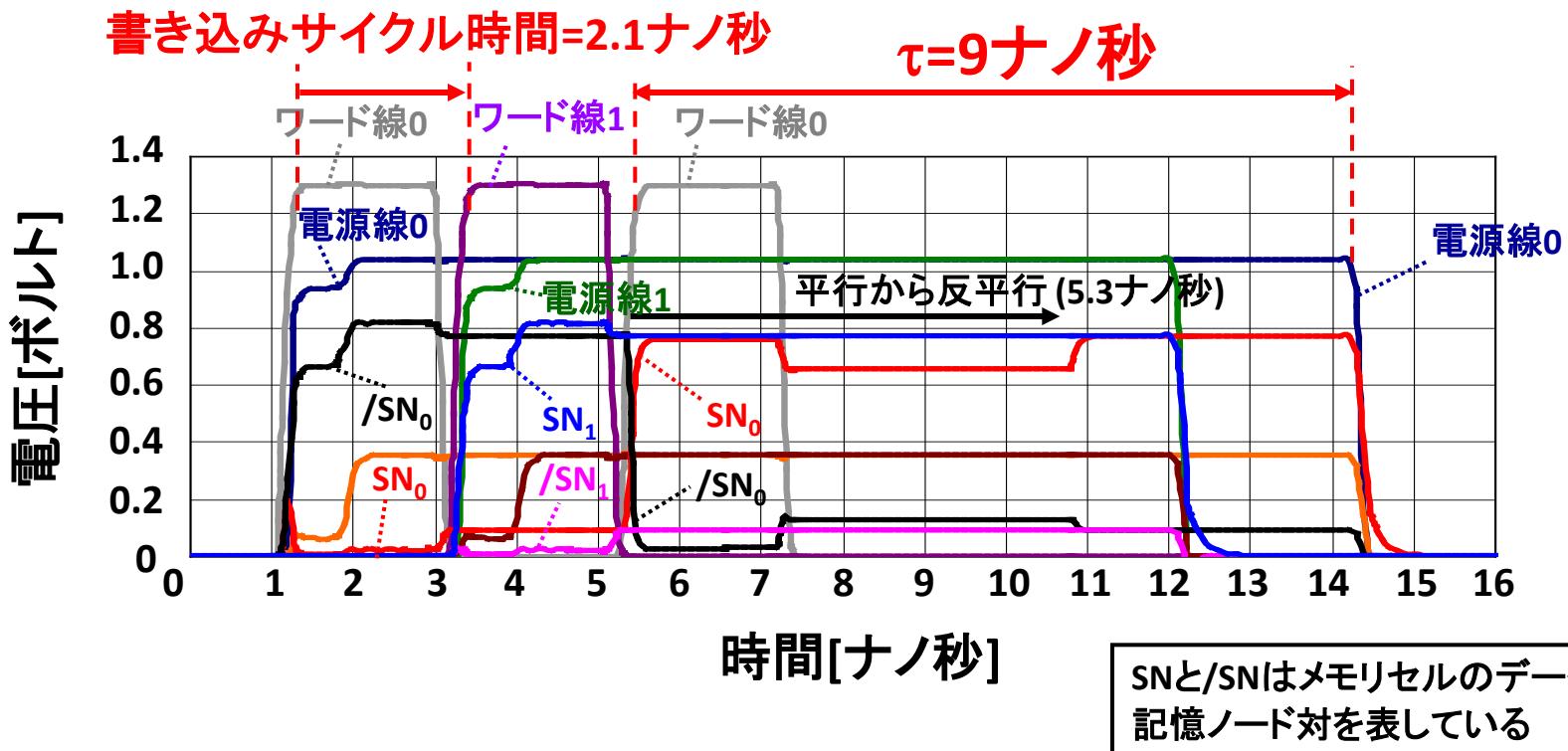

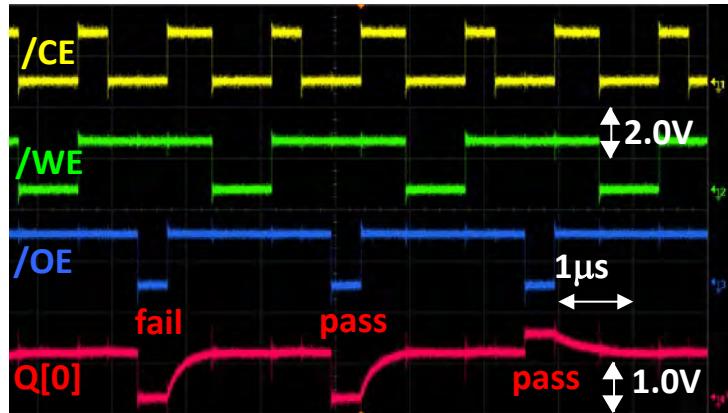

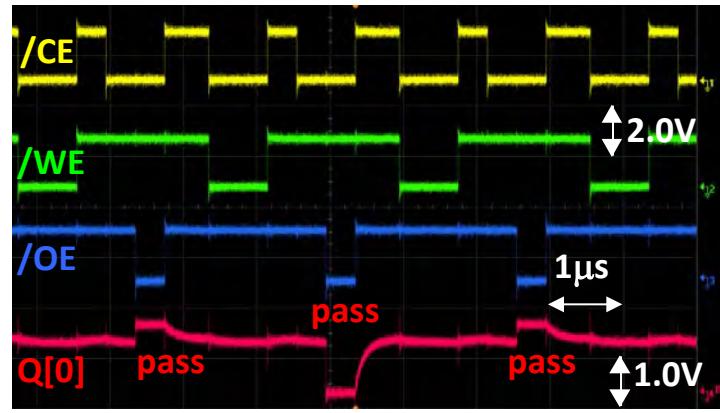

# 2.1ナノ秒で書き込み可能

L3キャッシュとしては十分な高速ランダムサイクル動作(2.1ナノ秒)

⇒ メモリ2(高信頼メモリ)に書き込む十分な時間(9ナノ秒)の確保に成功。※メモリ2への書き込み必要時間=5.3ナノ秒

90ナノメートル CMOS + 100ナノメートル 直径・垂直磁化型MTJ

## 電源電圧1.3Vでセルの動作

$$V_{dd} = 1.2V$$

読み出し ↔ 書込み

“1” 書込み ↔ “0” 書込み ↔ “1” 書込み

$$V_{dd} = 1.3V$$

読み出し ↔ 書込み

“1” 書込み ↔ “0” 書込み ↔ “1” 書込み

電源電圧が1.3Vにおいて、提案セルの動作確認に成功した。

# 今回の成果のまとめ

MTJを高速にスイッチングさせる時の課題を回避する

回路技術である**新しいバックグラウンド書き込みを開発**

6T-2MTJセルとタイマー内蔵型電源制御回路を搭載

した高速・大容量の1Mビット不揮発性ロジック混載メ

モリを開発した。

○ 高信頼な不揮発性性能と2.1ナノ秒という世界最高

速の書き込みサイクル時間を同時に実現した。

本提案技術により不揮発性性能による待機電力ゼロ

化と、高速メモリによるシステムの高性能化を同時に

実現できる基盤技術を構築した。

# 将来への展望

2011年12月 (IEDM2011)

世界最高速となる600MHz動作の不揮発性ラッチ回路の開発に成功し、パイプライン方式に適した不揮発性ロジックの道を開いた。

前回 (VLSI Symp2012)

世界最高速となる1nsec/200psecでのモード切替(アクセス ⇄ 待機状態)可能な待機電力ゼロ1Mビット混載メモリの開発に成功

今回 (VLSI Symp2013)

モバイルシステムに要求される高速動作性と待機電力ゼロ化(高信頼な不揮発性能)を両立させる新しい1Mビットメモリの開発に成功

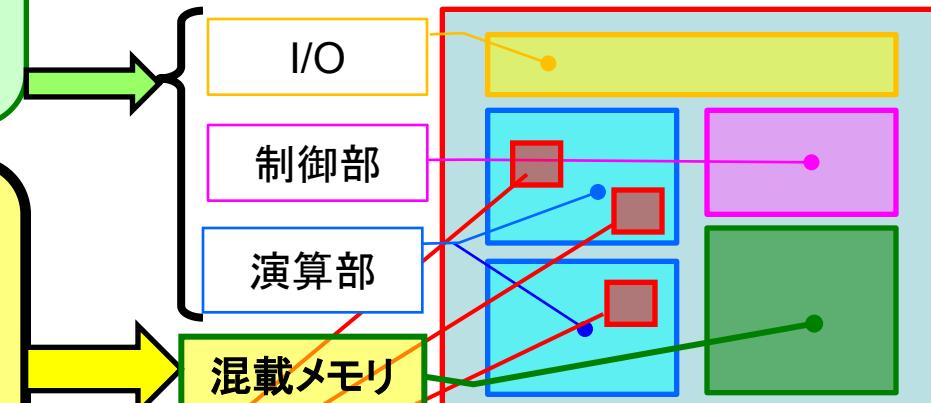

## 電子機器の頭脳：ロジックLSI

メモリと演算器等を1チップに内蔵し、1チップでコンピュータシステムを構成。

さまざまな応用分野の頭脳として利用

電気自動車

携帯

ルータ

(network)

データ

センター

医療機器

高速・低消費電力不揮発性混載メモリ実現の可能性

→ 待機電力ゼロ電子システムの実現への道が拓ける

東北大学

NEC

# 補助資料

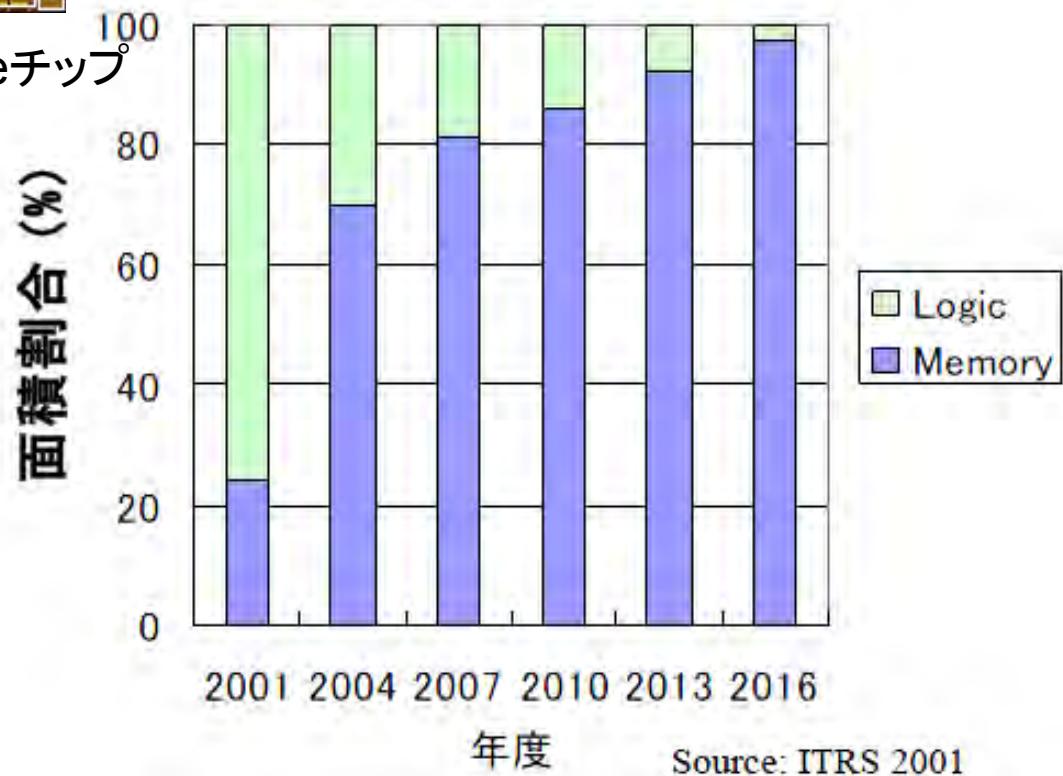

# マルチコア化による混載メモリの大容量化

Intel社製 Core i7-980X Extremeチップ

システムLSIにおける混載メモリの割合は増え続けている

## SoC上の Memory 素子面積率