東北大学

Empowered by Innovation

スピントロニクス技術を用いた

ロジックインメモリ集積回路の自動設計技術を開発

～消費電力を1/4に削減した画像処理プロセッサを動作実証～

2013年2月19日

国立大学法人東北大学

日本電気株式会社

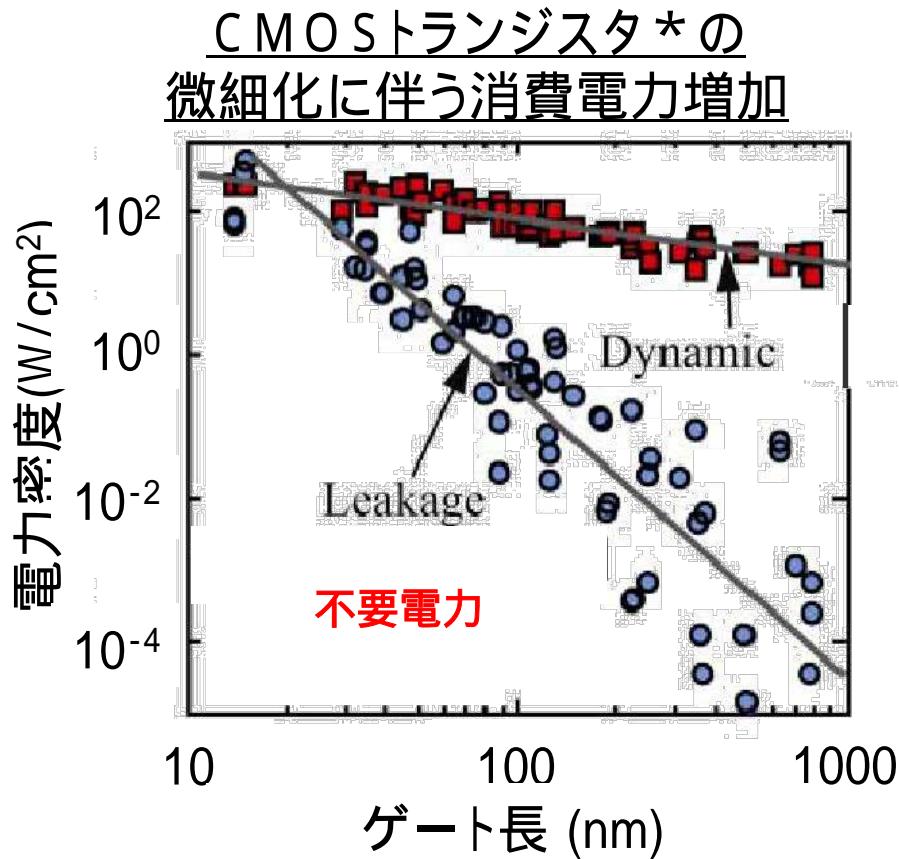

# 背景

E. Pop, *Nano Research*, vol.3, pp. 147-169, 2010

\* 通常の集積回路はCMOSトランジスタで構成

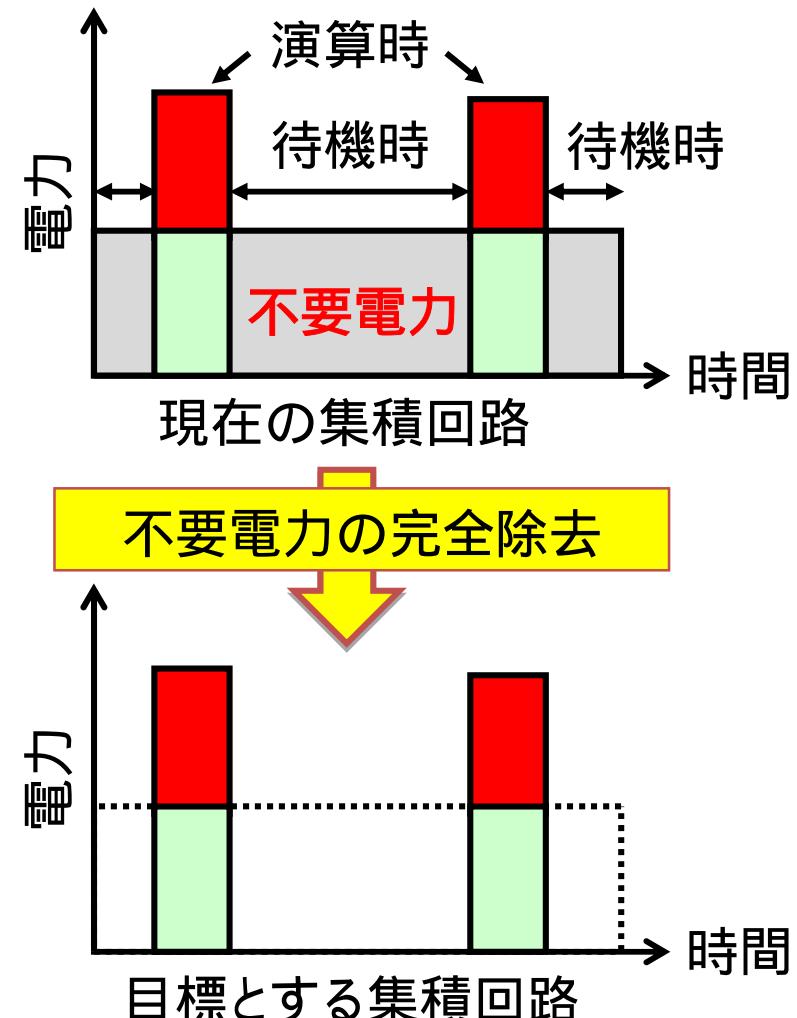

不要電力を除去するための仕組みを組み込むことで

省電力な電子機器を実現

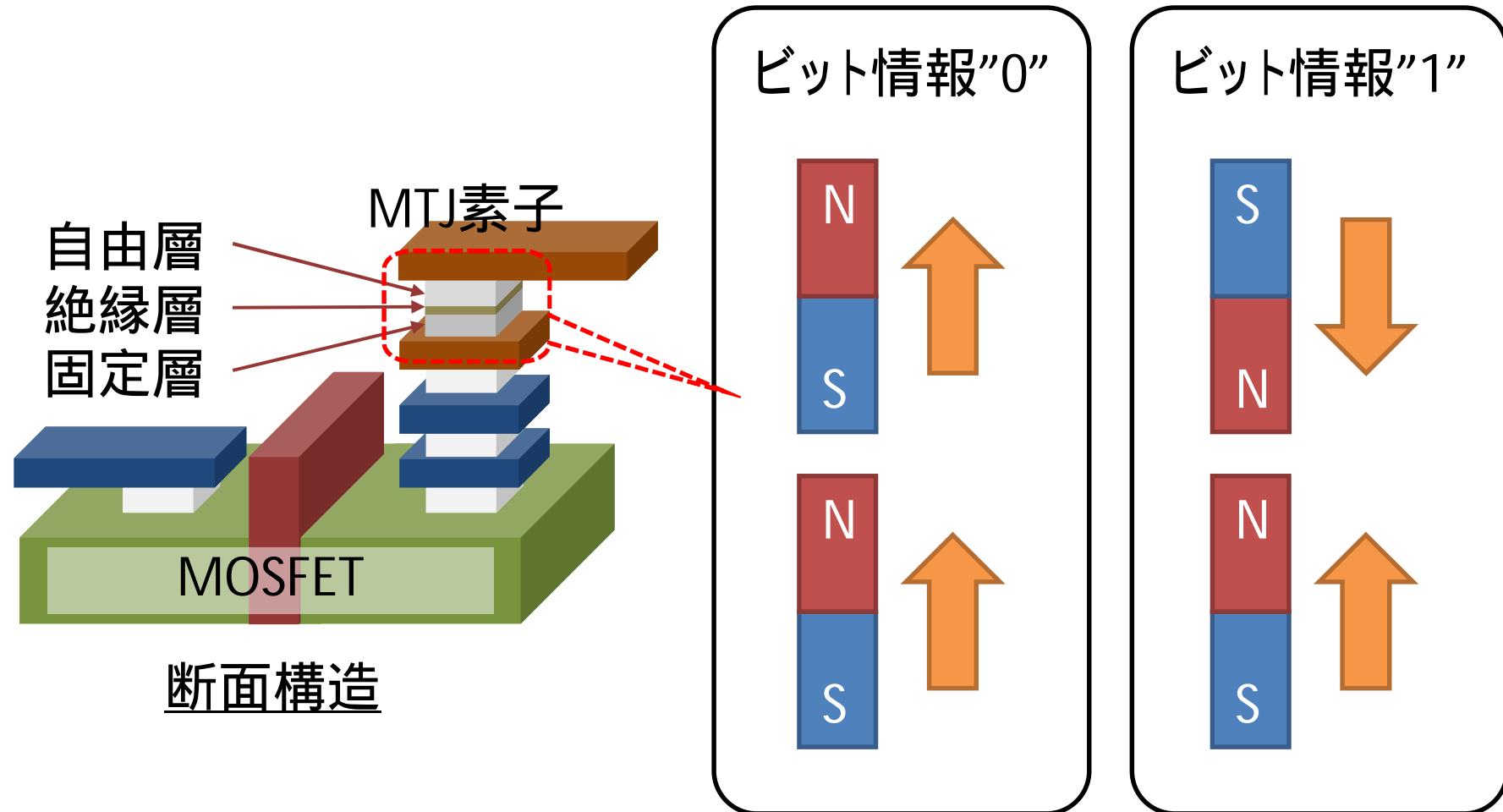

# MTJ素子を用いた不揮発LSI

磁性体の性質を有するMTJ素子を回路に組み込むことで

内部状態を不揮発的に保持 きめ細やかな電源遮断・復帰が可能

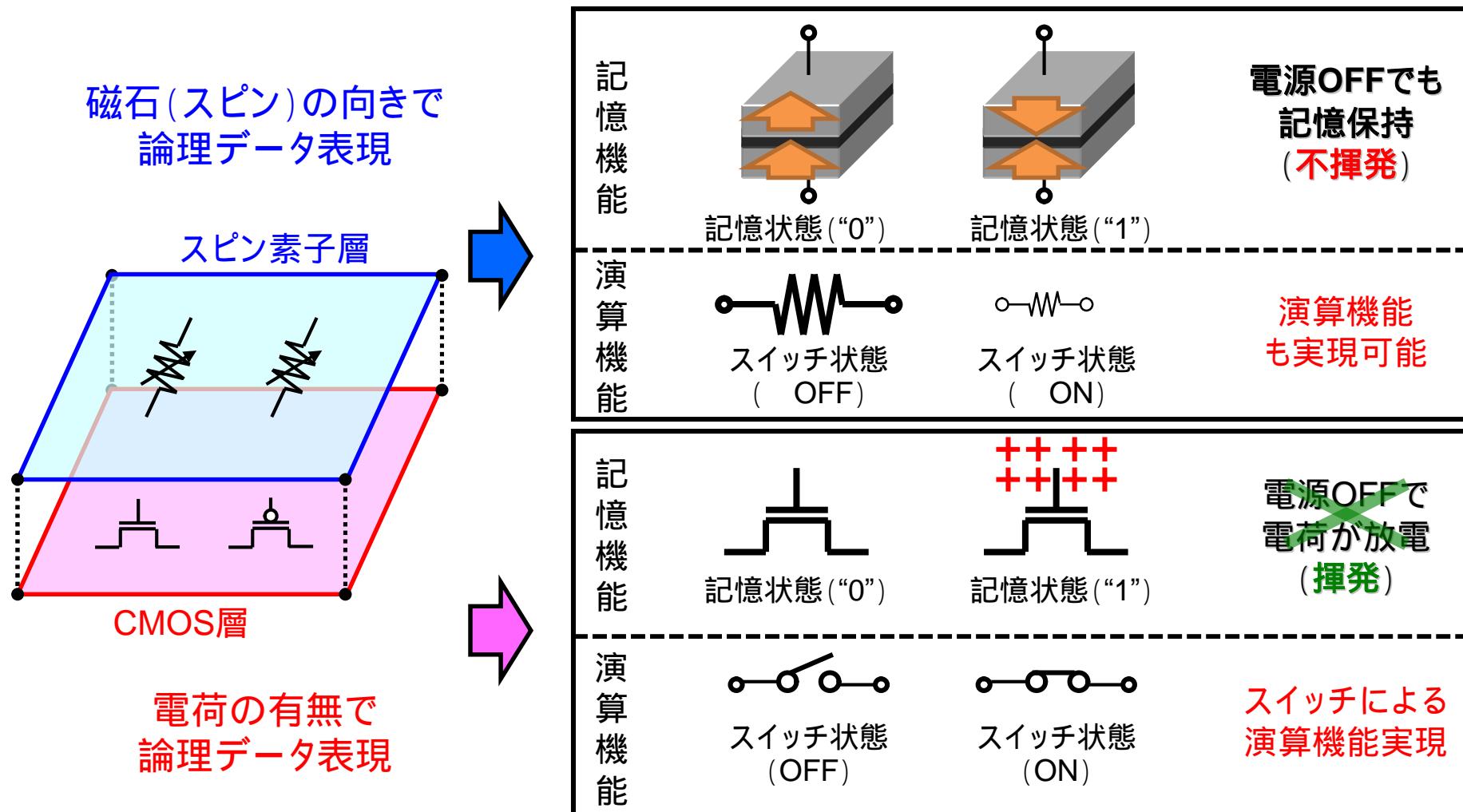

# スピノンによる回路の高機能化の原理

電荷(演算)とスピノン(記憶、演算)の両方利用 ➡ 電源OFFと記憶保持を両立

不揮発論理回路

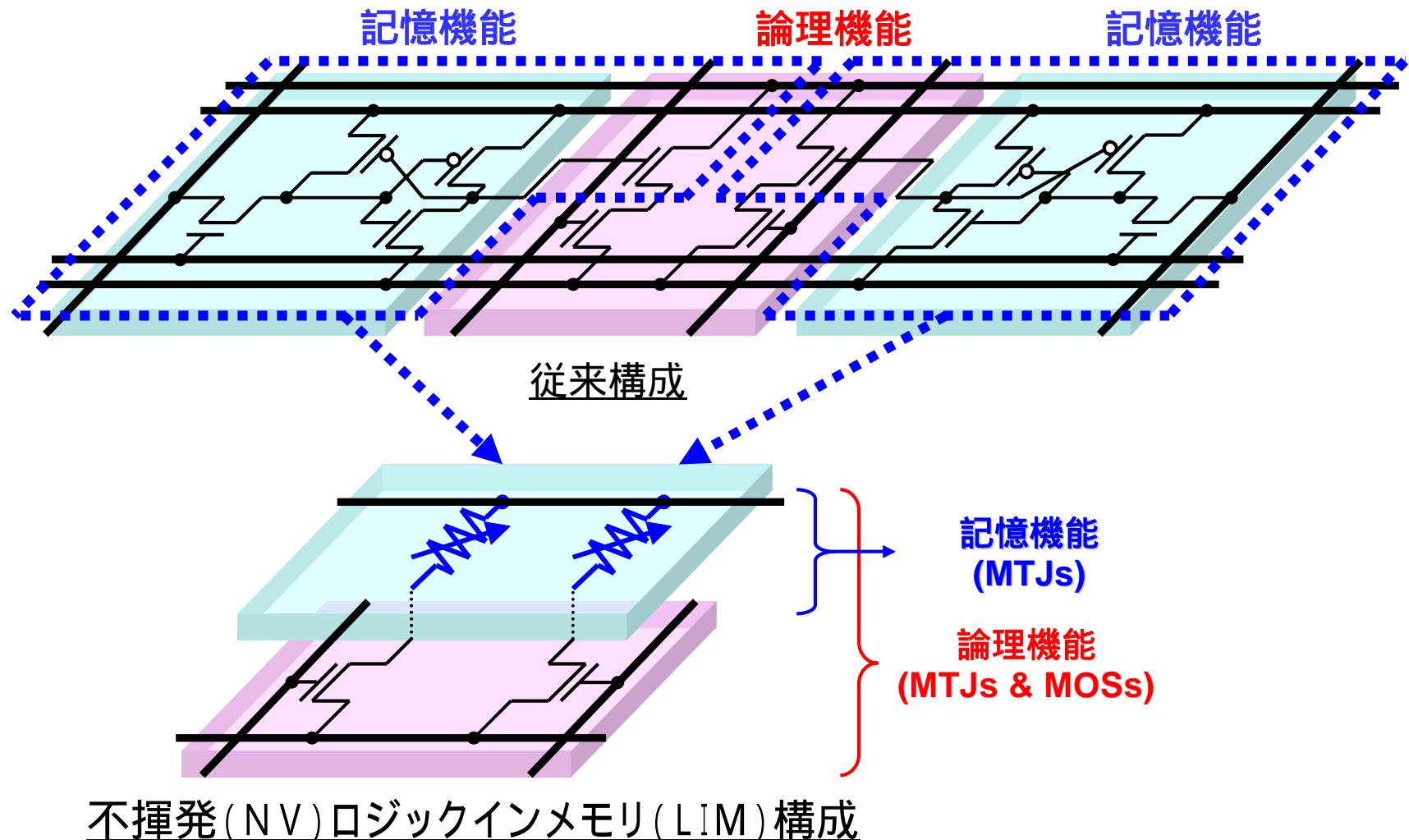

# 不揮発ロジックインメモリ回路(例:TCAMセル)

記憶・演算一体化(=ロジックインメモリ)により、コンパクトな不揮発回路を実現

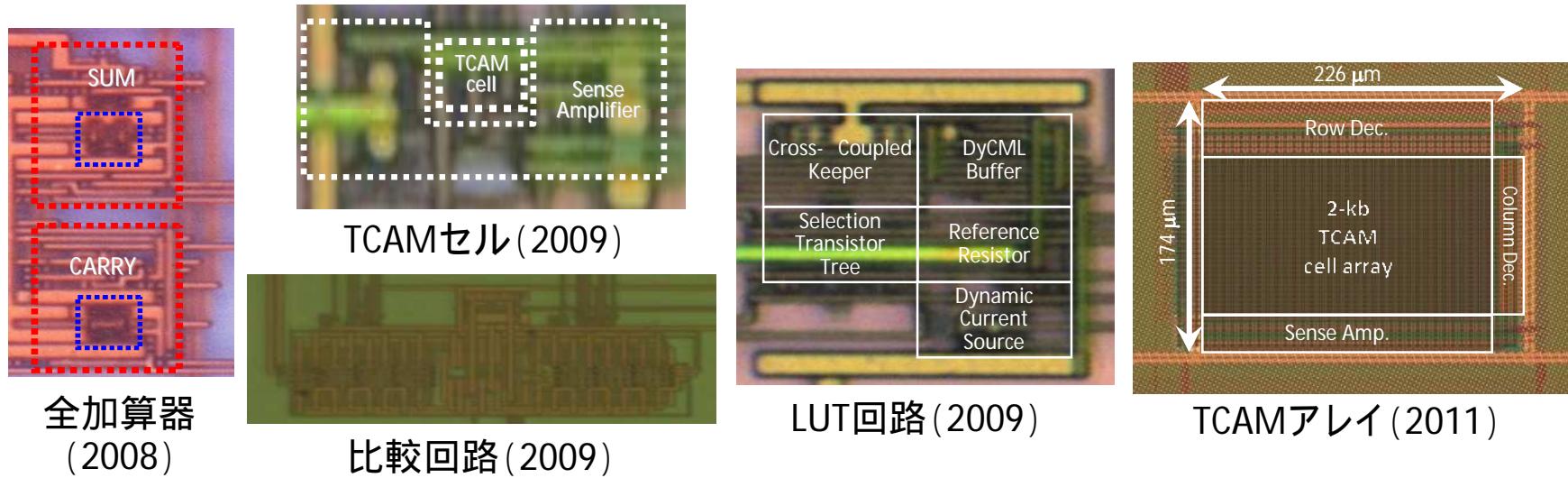

# 実用規模 NV-LIM LSI の実現に向けて

今まで開発されたロジックインメモリLSIの例

現状、NV-LIM LSI の設計は技術者による手設計が基本

( 繰返し性の高い回路でもレイアウト設計のみで3~4人月 )

**実用規模の汎用NV-LIM LSIの実現のためには

従来CMOS設計と互換の上位設計フローの確立が重要**

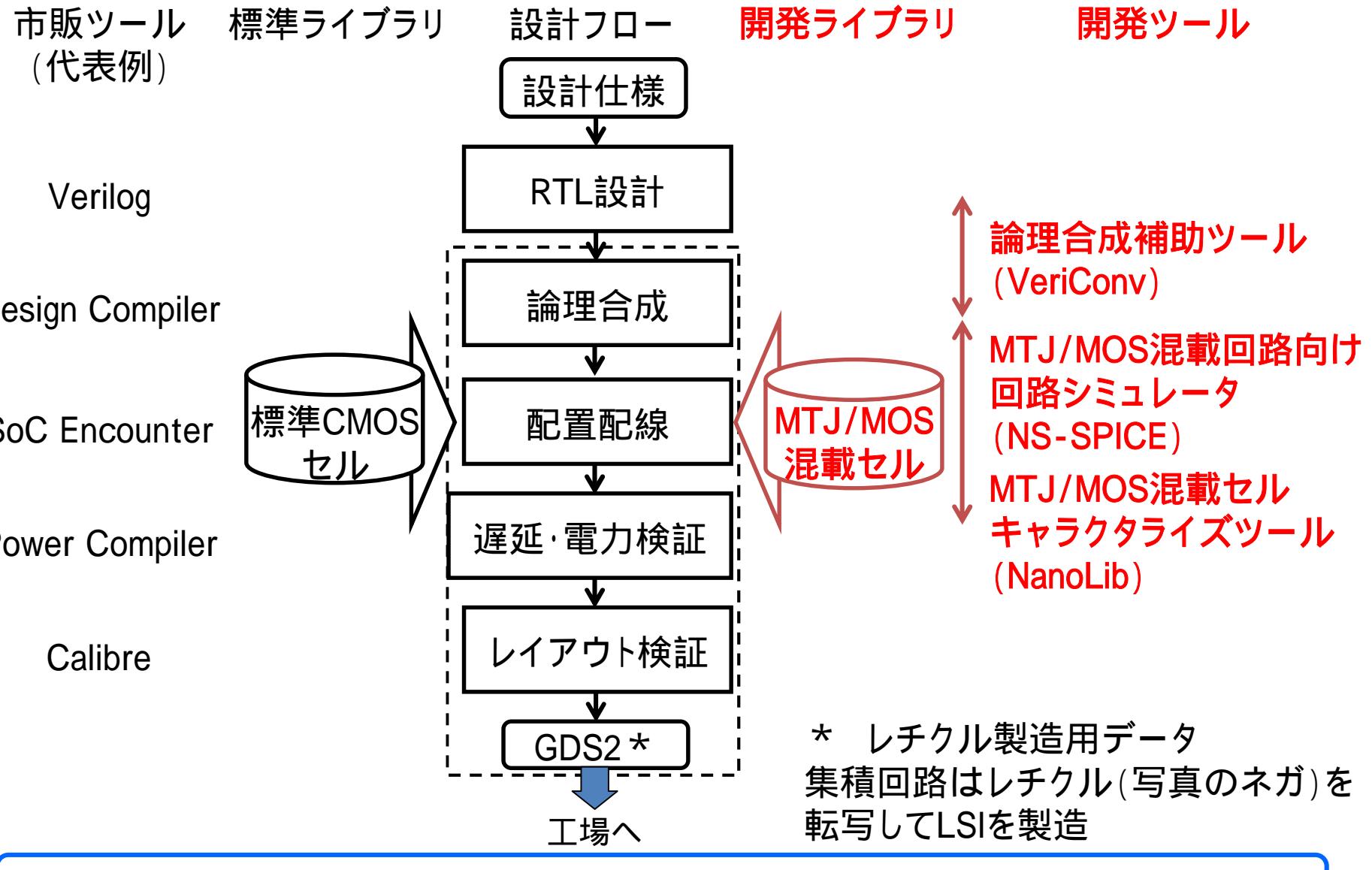

# 構築した自動設計フロー

\* レチクル製造用データ

集積回路はレチクル(写真のネガ)を

転写してLSIを製造

補助ツール＆ライブラリを従来フローに追加することで実現

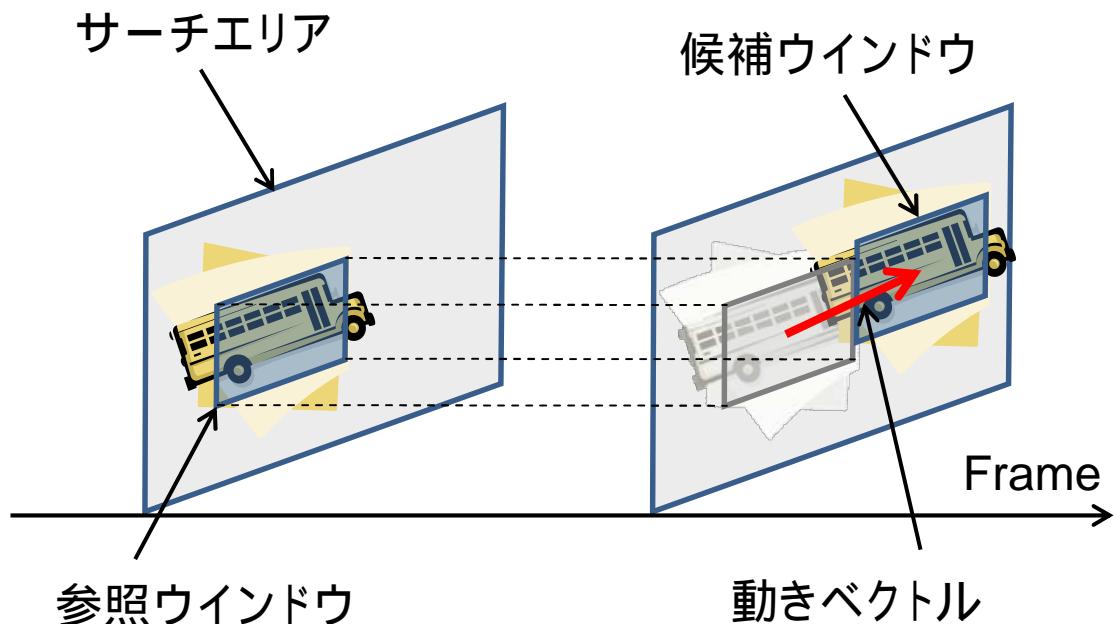

# 画像処理用アレイプロセッサ (動きベクトル検出回路)

動画像中の物体の動き量を推定するために用いる 動画圧縮

参照ウィンドウとの類似度計算

…絶対値差分和(Sum of Absolute Difference : SAD)

$$SAD(x, y) = \sum_i \sum_j |a_{i,j} - b_{x+i, y+j}|$$

ポータブルビデオ機器などの分野において画像処理プロセッサの

低電力化・高効率化が求められている

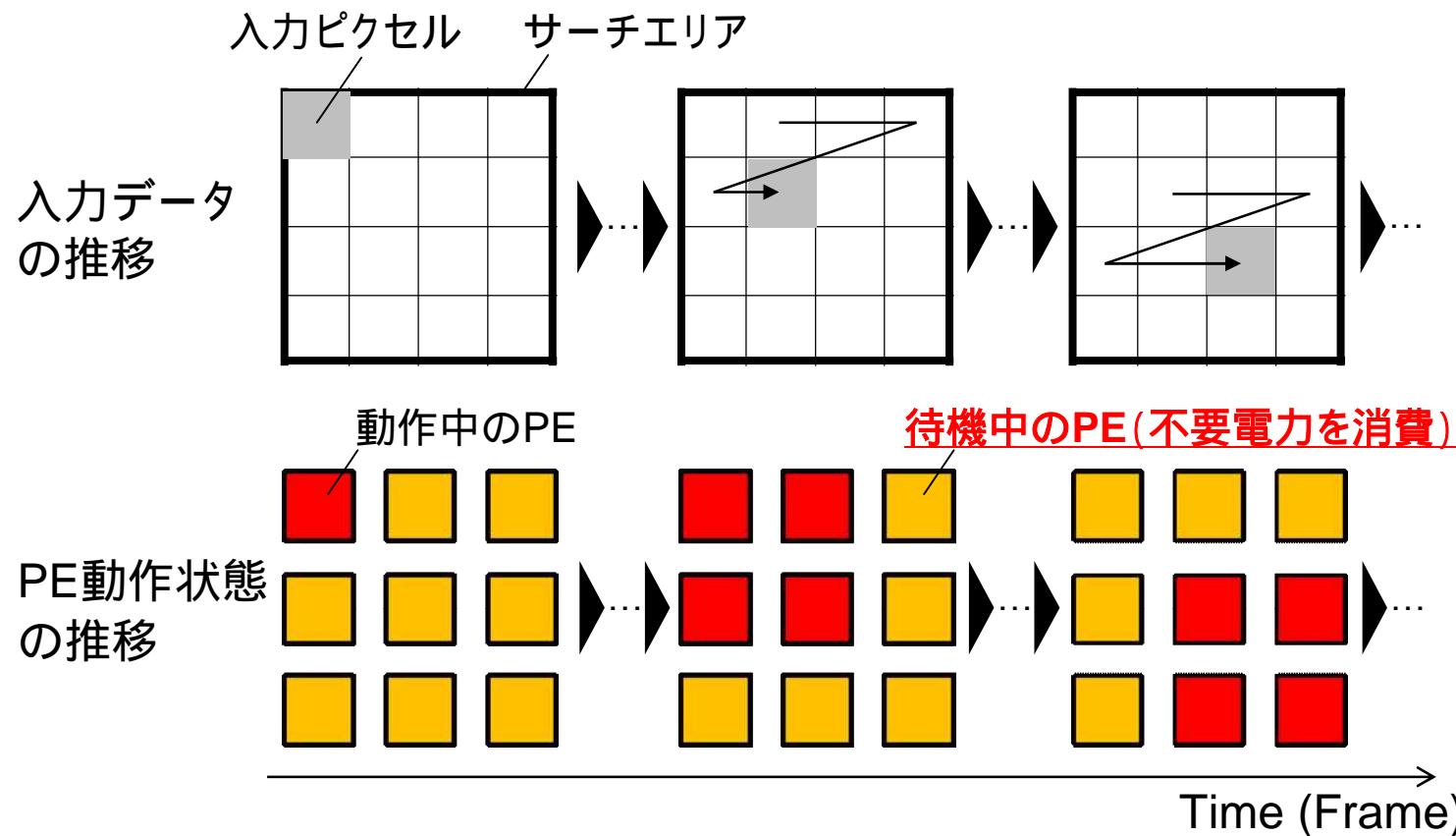

# 動作の様子

入力データに応じ動作中と待機中のPEが存在 不要電力を消費

待機中のPEへの電源供給を止めることで無駄な電力消費をカット

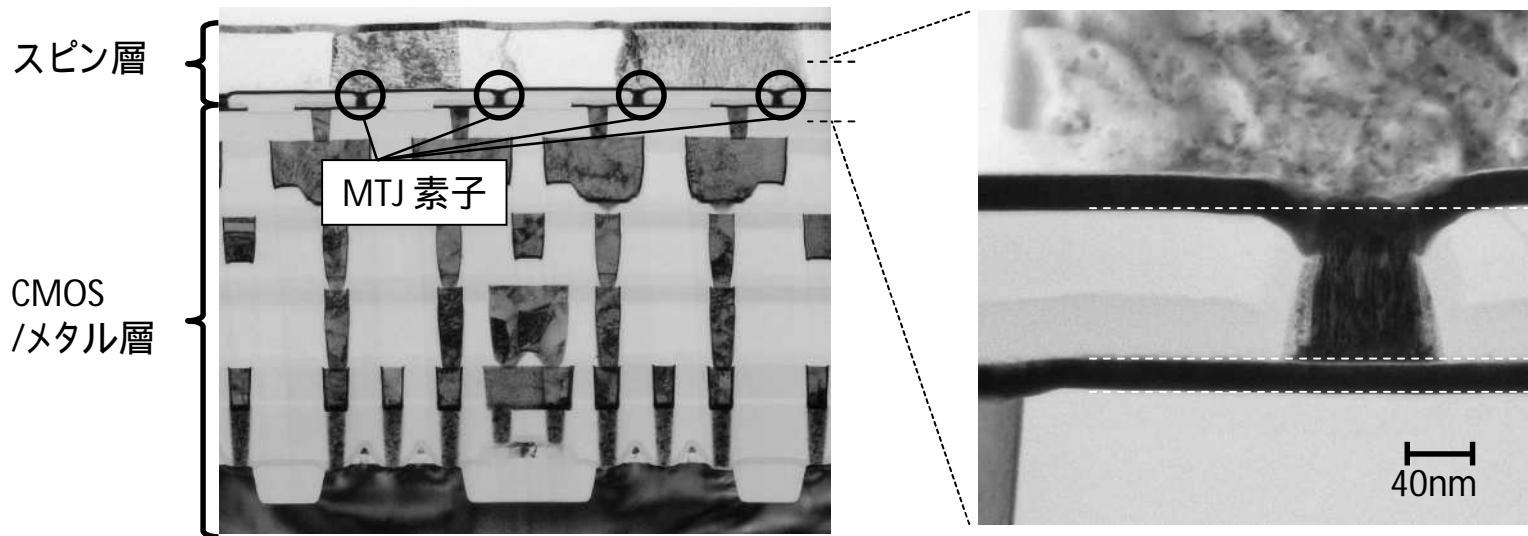

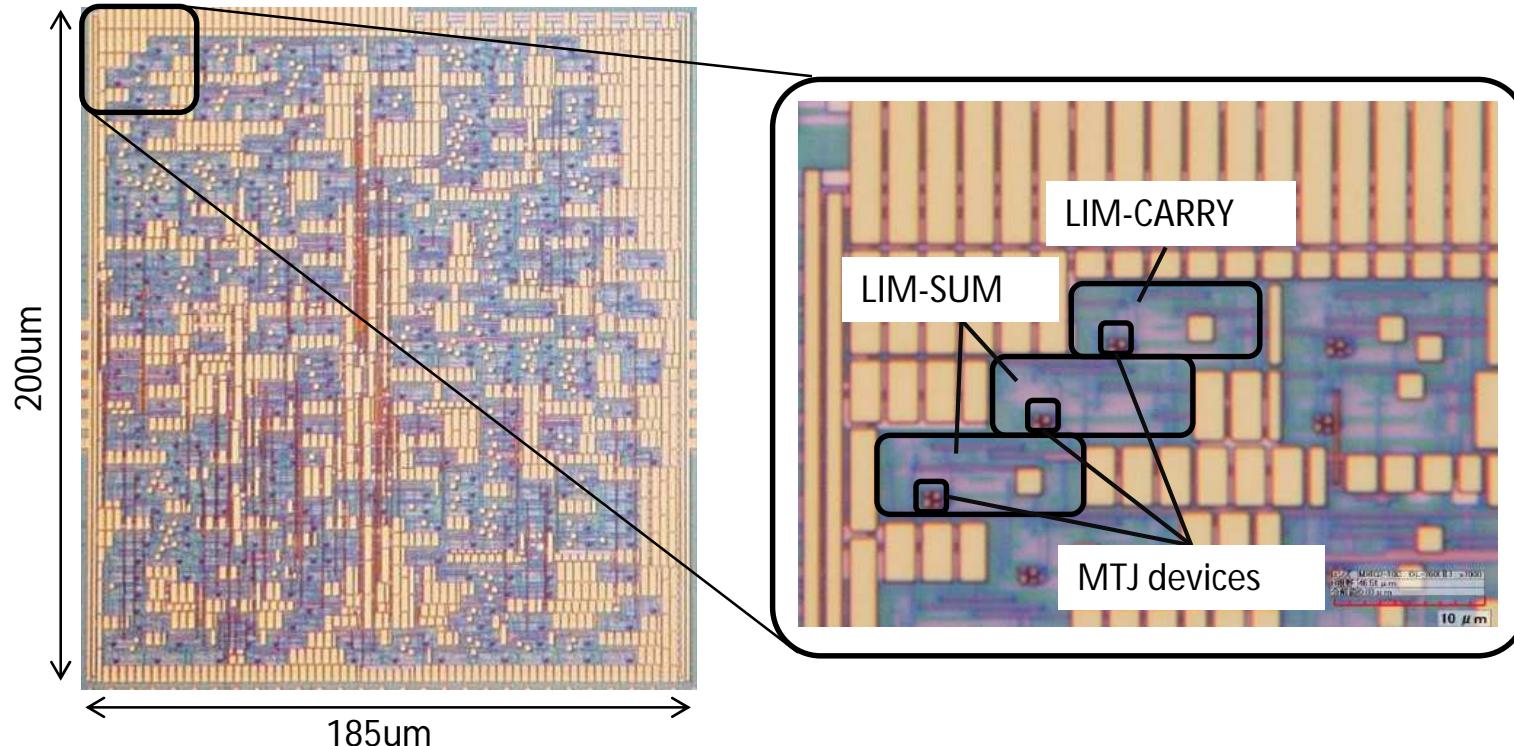

# 試作チップの顕微鏡写真と断面写真

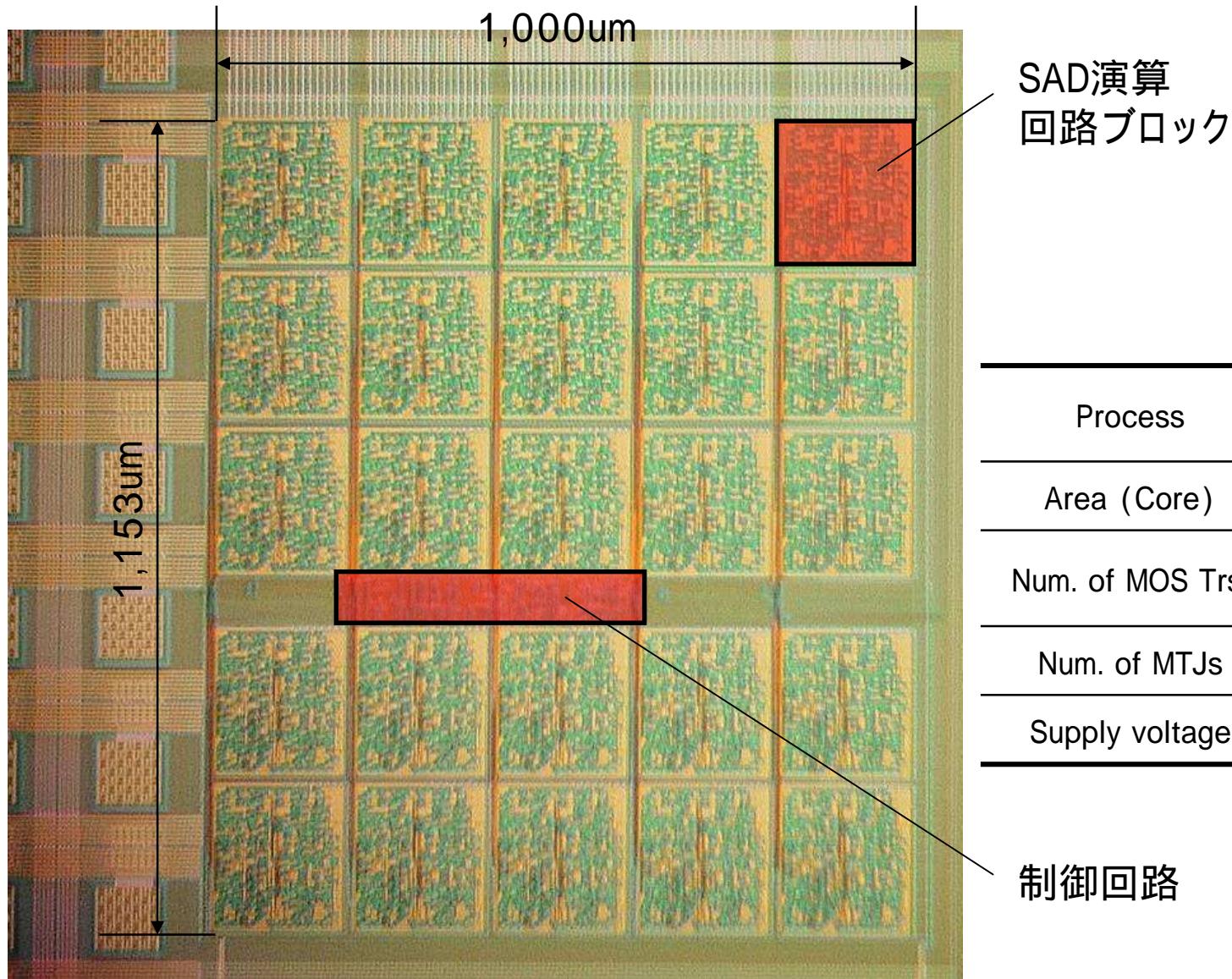

# 試作チップ全体写真

|                  |                       |

|------------------|-----------------------|

| Process          | 90nm<br>MTJ / MOS     |

| Area (Core)      | 1.153 mm <sup>2</sup> |

| Num. of MOS Trs. | 474,019               |

| Num. of MTJs     | 13,400                |

| Supply voltage   | 1.0 V                 |

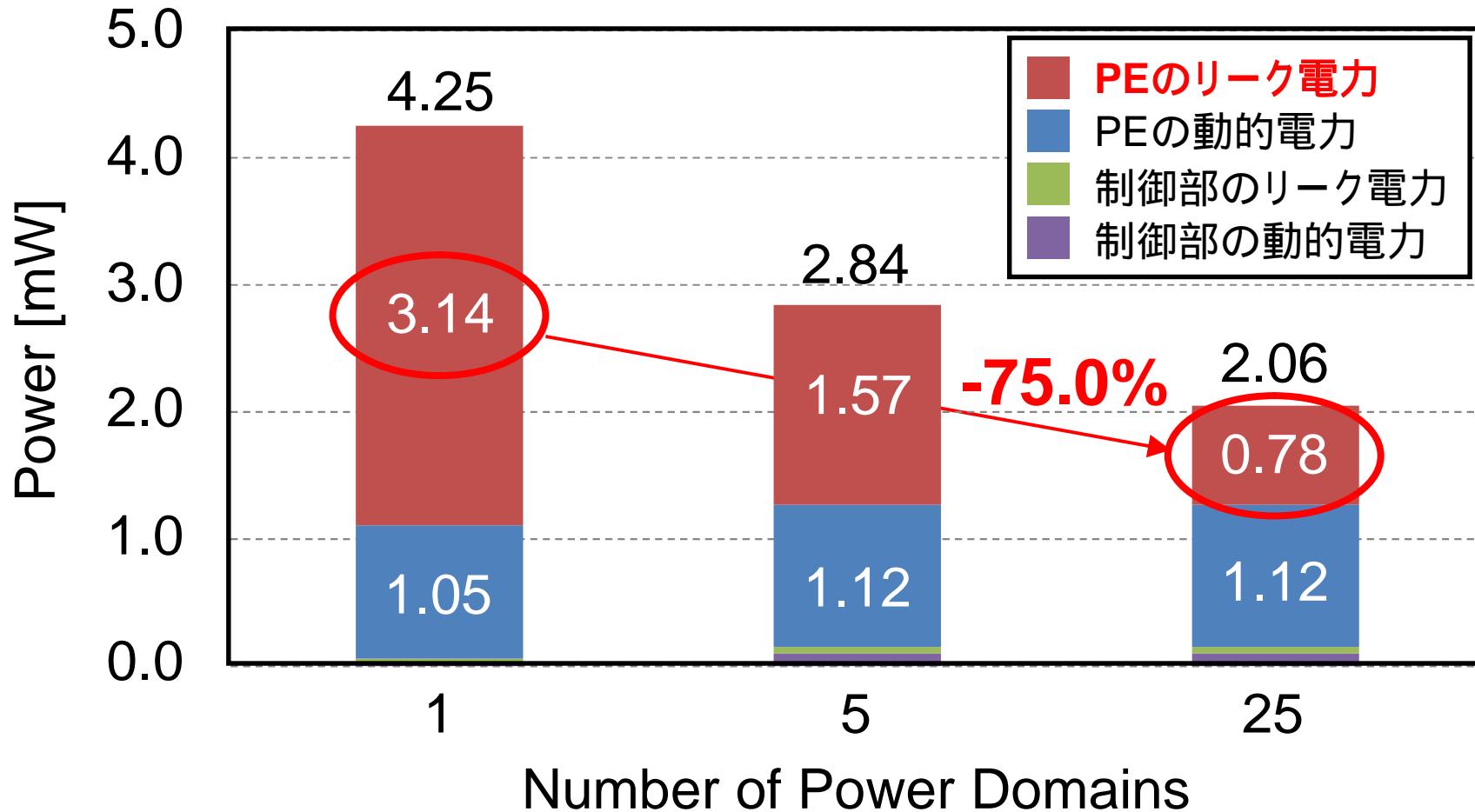

# 性能評価

回路をいくつかの領域に分け電源供給を細かく制御することにより

不要な電力消費を75%削減

# まとめ

- ・電子機器の待機電力ゼロに向けたスピントロニクス技術を論理集積回路に導入し、論理回路とメモリを一体化した不揮発性ロジックインメモリ集積回路を自動設計できるライブラリを開発

- ・本ライブラリを利用して、画像処理用のプロセッサを設計・試作し、演算時に不要な消費電力を $1/4$ に削減できることを実証

スピントロニクス論理集積回路技術をさらに向上して、

より大規模、省電力で、多用途な集積回路の開発を目指す